**DATASHEET**

### **Description**

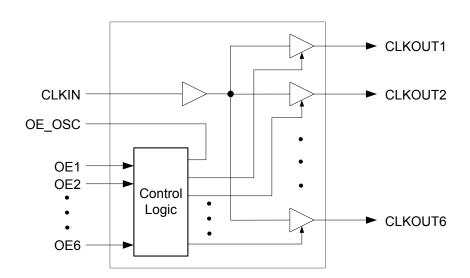

The 5PB12xx is a high-performance TCXO/LVCMOS clock fanout buffer family with individual OE pin for each output. The CLKIN pin can accept either a square wave (LVCMOS) or clipped sine wave (such as TCXO clipped sine wave output) as input.

There are 3 different fan-out versions available: 1:3, 1:4 and 1:6.

The 5PB12xx has industry-leading low jitter and extremely low current consumption, making it ideal for smart mobile devices.

## **Typical Applications**

- Smart Mobile Handsets

- RF and baseband peripheral clock distribution

- Automotive

### **Features**

- Extremely low operating and standby current consumption

- · Low RMS additive phase jitter

- Family supports 1.8V to 3.3V power supply voltage:

- For 1.8V supply: 5PB1203, 5PB1204, 5PB1206

- For 2.5V / 3.3V supply: 5PB1213, 5PB1214, 5PB1216

- Three, four, and six outputs with individual Output Enable pin

- One input

- OE\_OSC control pin to enable/disable reference TCXO/XO

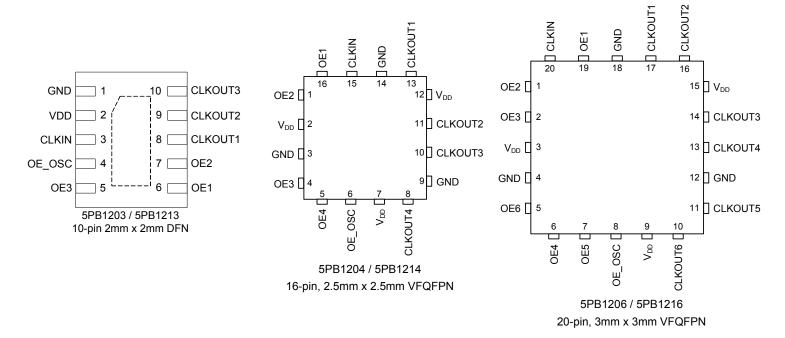

- Small 10-pin, 16-pin and 20-pin packages available

- Industrial -40° to +105°C temperature range

### **Block Diagram**

1

## **Pin Assignments**

## **Pin Descriptions**

|          |                    | Pin Numbe          | r                  |                                                 |                                                                                                                                                                                       |

|----------|--------------------|--------------------|--------------------|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name | 5PB1203<br>5PB1213 | 5PB1204<br>5PB1214 | 5PB1206<br>5PB1216 | Pin Type                                        | Pin Description                                                                                                                                                                       |

| VDD      | 2                  | 2, 7, 12           | 3, 9, 15           | Power                                           | Connect 1.8V to 5PB1203/5PB1204/5PB1206. Connect 2.5V or 3.3V to 5PB1213/5PB1214/5PB1216.                                                                                             |

| GND      | 1                  | 3, 9, 14           | 4, 12, 18          | Power                                           | Power supply ground.                                                                                                                                                                  |

| CLKIN    | 3                  | 15                 | 20                 | Input                                           | Reference input pin. Connect to LVCMOS input or TCXO.                                                                                                                                 |

| OE_OSC   | 4                  | 6                  | 8                  | Output                                          | Input Crystal Oscillator enable pin. Follow Enable Function Truth Table.  If all OE pins are low then OE_OSC is low. Otherwise OE_OSC is high, enabling reference crystal oscillator. |

| OE1      | 6                  | 16                 | 19                 | Input                                           | Output Enable pin for CLKOUT1. Active High. Internal 120k $\Omega$ pull-down.                                                                                                         |

| OE2      | 7                  | 1                  | 1                  | Input                                           | Output Enable pin for CLKOUT2. Active High. Internal 120kΩ pull-down.                                                                                                                 |

| OE3      | 5                  | 4                  | 2                  | Input                                           | Output Enable pin for CLKOUT3. Active High. Internal 120kΩ pull-down.                                                                                                                 |

| OE4      | _                  | 5                  | 6                  | Input                                           | Output Enable pin for CLKOUT4. Active High. Internal 120kΩ pull-down.                                                                                                                 |

| OE5      | _                  | _                  | 7                  | Input                                           | Output Enable pin for CLKOUT5. Active High. Internal 120kΩ pull-down.                                                                                                                 |

| OE6      | _                  | _                  | 5                  | Input                                           | Output Enable pin for CLKOUT6. Active High. Internal 120kΩ pull-down.                                                                                                                 |

| CLKOUT1  | 8                  | 13                 | 17                 | Output                                          | Clock Output 1. Same frequency as CLKIN.                                                                                                                                              |

| CLKOUT2  | 9                  | 11                 | 16                 | Output                                          | Clock Output 2. Same frequency as CLKIN.                                                                                                                                              |

| CLKOUT3  | 10                 | 10                 | 14                 | Output Clock Output 3. Same frequency as CLKIN. |                                                                                                                                                                                       |

| CLKOUT4  | _                  | 8                  | 13                 | Output                                          | Clock Output 4. Same frequency as CLKIN.                                                                                                                                              |

| CLKOUT5  | _                  | _                  | 11                 | Output                                          | Clock Output 5. Same frequency as CLKIN.                                                                                                                                              |

| CLKOUT6  | _                  | _                  | 10                 | Output                                          | Clock Output 6. Same frequency as CLKIN.                                                                                                                                              |

### **Enable Function Truth Table**

|     | Input |     |     |     |     | Output |         |         |         |         |         |         |

|-----|-------|-----|-----|-----|-----|--------|---------|---------|---------|---------|---------|---------|

| OE1 | OE2   | OE3 | OE4 | OE5 | OE6 | OE_OSC | CLKOUT1 | CLKOUT2 | CLKOUT3 | CLKOUT4 | CLKOUT5 | CLKOUT6 |

| 0   | 0     | 0   | 0   | 0   | 0   | 0      | Hi-Z    | Hi-Z    | Hi-Z    | Hi-Z    | Hi-Z    | Hi-Z    |

| 1   | 0     | 0   | 0   | 0   | 0   | 1      | CLOCK   | Hi-Z    | Hi-Z    | Hi-Z    | Hi-Z    | Hi-Z    |

| 1   | 1     | 0   | 0   | 0   | 0   | 1      | CLOCK   | CLOCK   | Hi-Z    | Hi-Z    | Hi-Z    | Hi-Z    |

|     |       |     |     |     |     |        |         |         |         |         |         |         |

| 1   | 1     | 1   | 1   | 1   | 1   | 1      | CLOCK   | CLOCK   | CLOCK   | CLOCK   | CLOCK   | CLOCK   |

### **External Components**

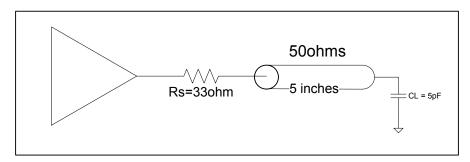

A minimum number of external components are required for proper operation. A decoupling capacitor of  $0.01\mu F$  should be connected between VDD on pin 1 and GND on pin 4, as close to the device as possible. A  $33\Omega$  series terminating resistor may be used on each clock output if the trace is longer than 1 inch.

To achieve the low output skew that the 5PB12xx is capable of, careful attention must be paid to board layout. Essentially, all four outputs must have identical terminations, identical loads and identical trace geometries. If they do not, the output skew will be degraded. For example, using a  $30\Omega$  series termination on one output (with  $33\Omega$  on the others) will cause at least 15ps of skew.

### **Absolute Maximum Ratings**

Stresses above the ratings listed below can cause permanent damage to the 5PB12xx. These ratings, which are standard values for IDT commercially rated parts, are stress ratings only. Functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods can affect product reliability. Electrical parameters are guaranteed only over the recommended operating temperature range.

| Item                                     | Rating                |

|------------------------------------------|-----------------------|

| Supply Voltage, VDD                      | 3.8V                  |

| Output Enable and All Inputs/Outputs     | -0.5 V to VDD + 0.5 V |

| Ambient Operating Temperature (extended) | -40 to +105°C         |

| Storage Temperature                      | -65 to +150°C         |

| Junction Temperature                     | 125°C                 |

| Soldering Temperature                    | 260°C                 |

### **DC Electrical Characteristics**

(VDD = 1.8V, 2.5V, 3.3V)

**VDD = 1.8V \pm5%**, for **5PB1203 / 1204 / 1206**, ambient temperature -40° to +105°C, unless stated otherwise.

| Parameter                 | Symbol          | Conditions                                | Min.        | Тур.  | Max.        | Units |

|---------------------------|-----------------|-------------------------------------------|-------------|-------|-------------|-------|

| Operating Voltage         | VDD             |                                           | 1.71        |       | 1.89        | V     |

| Input High Voltage, CLKIN | V <sub>IH</sub> | LVCMOS input. Note 1                      | VDD/2 + 200 |       | VDD         | mV    |

| Input Low Voltage, CLKIN  | V <sub>IL</sub> | LVCMOS input. Note 1                      |             |       | VDD/2 - 200 | mV    |

| Input High Voltage, OE    | V <sub>IH</sub> |                                           | 0.7xVDD     |       | VDD         | V     |

| Input Low Voltage, OE     | V <sub>IL</sub> |                                           |             |       | 0.3xVDD     | V     |

| Output High Voltage       | V <sub>OH</sub> | I <sub>OH</sub> = -4mA                    | 0.8xVDD     |       |             | V     |

| Output Low Voltage        | V <sub>OL</sub> | I <sub>OL</sub> = 4mA                     |             |       | 0.2xVDD     | V     |

| Nominal Output Impedance  | Z <sub>O</sub>  |                                           |             | 17    |             | Ω     |

| Input Capacitance         | C <sub>IN</sub> |                                           |             | 5     |             | pF    |

| Operating Supply Current  |                 |                                           |             |       |             |       |

| 5PB1203                   |                 | CLKIN = 26MHz, all outputs enabled        |             | 5.10  |             |       |

| 3FB1203                   |                 | CLKIN = Low or High, all outputs disabled |             | 0.02  | 0.03        |       |

| 5PB1204                   | IDD             | CLKIN = 26MHz, all outputs enabled        |             | 9.30  |             | m 1   |

| 3FB1204                   | טטו             | CLKIN = Low or High, all outputs disabled |             | 2.51  | 4           | mA    |

| 5PB1206                   |                 | CLKIN = 26MHz, all outputs enabled        |             | 11.90 |             |       |

| 0FB1200                   |                 | CLKIN = Low or High, all outputs disabled |             | 2.5   | 4           |       |

### **VDD = 2.5V \pm5%**, for **5PB1213 / 1214 / 1216**, ambient temperature -40° to +105°C, unless stated otherwise.

| Parameter                 | Symbol          | Conditions                                | Min.        | Тур. | Max.        | Units |

|---------------------------|-----------------|-------------------------------------------|-------------|------|-------------|-------|

| Operating Voltage         | VDD             |                                           | 2.375       |      | 2.625       | V     |

| Input High Voltage, CLKIN | V <sub>IH</sub> | LVCMOS input. Note 1                      | VDD/2 + 200 |      | VDD         | mV    |

| Input Low Voltage, CLKIN  | V <sub>IL</sub> | LVCMOS input. Note 1                      |             |      | VDD/2 - 200 | mV    |

| Input High Voltage, OE    | V <sub>IH</sub> |                                           | 0.7xVDD     |      | VDD         | V     |

| Input Low Voltage, OE     | V <sub>IL</sub> |                                           |             |      | 0.3xVDD     | V     |

| Output High Voltage       | V <sub>OH</sub> | I <sub>OH</sub> = -4mA                    | 0.8xVDD     |      |             | V     |

| Output Low Voltage        | V <sub>OL</sub> | I <sub>OL</sub> = 4mA                     |             |      | 0.2xVDD     | V     |

| Nominal Output Impedance  | Z <sub>O</sub>  |                                           |             | 17   |             | Ω     |

| Input Capacitance         | C <sub>IN</sub> | ICLK, OE pin                              |             | 5    |             | pF    |

| Operating Supply Current  |                 |                                           |             |      |             |       |

| 5PB1213                   |                 | CLKIN = 26MHz, all outputs enabled        |             | 6.68 |             |       |

| 3FB1213                   |                 | CLKIN = Low or High, all outputs disabled |             | 0.05 | 0.5         |       |

| 5PB1214                   | IDD             | CLKIN = 26MHz, all outputs enabled        |             | 10.2 |             | A     |

| 1 0 F D 1 Z 1 4           | IDD             | CLKIN = Low or High, all outputs disabled |             | 3.47 | 5           | - mA  |

| 5DD1216                   |                 | CLKIN = 26MHz, all outputs enabled        |             | 16.5 |             | 1     |

| 5PB1216                   |                 | CLKIN = Low or High, all outputs disabled |             | 3.50 | 5           | 1     |

**VDD = 3.3V \pm5%**, for **5PB1213 / 1214 / 1216**, ambient temperature -40° to +105°C, unless stated otherwise

| Parameter                 | Symbol          | Conditions                                | Min.        | Тур. | Max.        | Units |

|---------------------------|-----------------|-------------------------------------------|-------------|------|-------------|-------|

| Operating Voltage         | VDD             |                                           | 3.135       |      | 3.465       | V     |

| Input High Voltage, CLKIN | V <sub>IH</sub> | LVCMOS input. Note 1                      | VDD/2 + 200 |      | VDD         | mV    |

| Input Low Voltage, CLKIN  | V <sub>IL</sub> | LVCMOS input. Note 1                      |             |      | VDD/2 - 200 | mV    |

| Input High Voltage, OE    | V <sub>IH</sub> |                                           | 0.7xVDD     |      | VDD         | V     |

| Input Low Voltage, OE     | V <sub>IL</sub> |                                           |             |      | 0.3xVDD     | V     |

| Output High Voltage       | V <sub>OH</sub> | I <sub>OH</sub> = -4mA                    | 0.8xVDD     |      |             | V     |

| Output Low Voltage        | V <sub>OL</sub> | I <sub>OL</sub> = 4mA                     |             |      | 0.2xVDD     | V     |

| Nominal Output Impedance  | Z <sub>O</sub>  |                                           |             | 17   |             | Ω     |

| Input Capacitance         | C <sub>IN</sub> | ICLK, OE pin                              |             | 5    |             | pF    |

| Operating Supply Current  | 1               |                                           |             |      |             |       |

| 5PB1213                   |                 | CLKIN = 26MHz, all outputs enabled        |             | 9.10 |             |       |

| 3FB1213                   |                 | CLKIN = Low or High, all outputs disabled |             | 0.22 | 0.5         |       |

| EDD4244                   | IDD             | CLKIN = 26MHz, all outputs enabled        |             | 13.4 |             | - A   |

| 5PB1214                   | טטו             | CLKIN = Low or High, all outputs disabled |             | 4.28 | 7           | - mA  |

| 5PB1216                   | 1               | CLKIN = 26MHz, all outputs enabled        |             | 21.4 |             | 1     |

| 3FD1210                   |                 | CLKIN = Low or High, all outputs disabled |             | 4.60 | 7           |       |

Notes: 1. Nominal switching threshold is VDD/2.

### **AC Electrical Characteristics**

(VDD = 1.8V, 2.5V, 3.3V)

### **VDD = 1.8V \pm5%**; for **5PB1203 / 1204 / 1206**, ambient Temperature -40° to +105°C, unless stated otherwise

| Parameter                                                  | Symbol                            | Conditions                                                               | Min. | Тур. | Max. | Units  |

|------------------------------------------------------------|-----------------------------------|--------------------------------------------------------------------------|------|------|------|--------|

| Input Frequency                                            |                                   |                                                                          | 0    |      | 200  | MHz    |

| Output Rise Time                                           | t <sub>OR</sub>                   | 0.36 to 1.44V, C <sub>L</sub> = 5pF                                      |      | 0.6  | 1.0  | ns     |

| Output Fall Time                                           | t <sub>OF</sub>                   | 1.44 to 0.36V, C <sub>L</sub> = 5pF                                      |      | 0.6  | 1.0  | ns     |

| Propagation Delay                                          | Note 1                            | Note 1                                                                   | 1.5  | 2.0  | 2.5  | ns     |

| Buffer Additive Phase Jitter, RMS                          |                                   | 26MHz TCXO clipped sine wave input,<br>Integration Range: 12kHz to 20MHz |      | 420  |      | fs     |

|                                                            |                                   | 125MHz LVCMOS input,<br>Integration Range: 12kHz to 20MHz                |      | 42   |      | fs     |

| Output to Output Skew                                      | t <sub>SKEWO-O</sub>              | Note 2, Rising edges at VDD/2                                            |      | 20   | 50   | ps     |

| Device to Device Skew                                      | t <sub>SKEWD-D</sub>              | Rising edges at VDD/2                                                    |      |      | 200  | ps     |

| Delay for Output Enable / Disable<br>Time ENABLEx to BCLKn | t <sub>EN</sub> /t <sub>DIS</sub> | CL < 5pF                                                                 |      |      | 3    | cycles |

| Start-up Time                                              | t <sub>START-UP</sub>             |                                                                          |      |      | 2    | ms     |

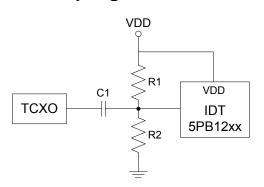

| TCXO Clock Clipped Sine Wave Input Voltage Swing Level     | VIN <sub>pp</sub>                 | VDD = 1.8V, should connect to CLKIN through AC coupling and bias circuit |      | 0.8  |      | V      |

### **VDD = 2.5V \pm5%**; for **5PB1213 / 1214 / 1216**, ambient Temperature -40° to +105°C, unless stated otherwise

| Parameter                                                  | Symbol                            | Conditions                                                               | Min. | Тур. | Max. | Units  |

|------------------------------------------------------------|-----------------------------------|--------------------------------------------------------------------------|------|------|------|--------|

| Input Frequency                                            |                                   |                                                                          | 0    |      | 200  | MHz    |

| Output Rise Time                                           | t <sub>OR</sub>                   | 0.5 to 2.0V, C <sub>L</sub> = 5pF                                        |      | 0.6  | 1.0  | ns     |

| Output Fall Time                                           | t <sub>OF</sub>                   | 2.0 to 0.5V, C <sub>L</sub> = 5pF                                        |      | 0.6  | 1.0  | ns     |

| Propagation Delay                                          | Note 1                            | Note 1                                                                   | 1.7  | 2.2  | 2.7  | ns     |

| Buffer Additive Phase Jitter, RMS                          |                                   | 26MHz TCXO clipped sine wave input,<br>Integration Range: 12kHz to 20MHz |      | 280  |      | fs     |

|                                                            |                                   | 125MHz LVCMOS input,<br>Integration Range: 12kHz to 20MHz                |      | 30   |      | fs     |

| Output to Output Skew                                      | t <sub>SKEWO-O</sub>              | Note 2, Rising edges at VDD/2                                            |      | 20   | 50   | ps     |

| Device to Device Skew                                      | t <sub>SKEWD-D</sub>              | Rising edges at VDD/2                                                    |      |      | 200  | ps     |

| Delay for Output Enable / Disable<br>Time ENABLEx to BCLKn | t <sub>EN/</sub> t <sub>DIS</sub> | CL < 5pF                                                                 |      |      | 3    | cycles |

| Start-up Time                                              | t <sub>START-UP</sub>             | Part start-up time for valid outputs after VDD ramp-up                   |      |      | 2    | ms     |

| TCXO Clock Clipped Sine Wave Input Voltage Swing Level     | VIN <sub>pp</sub>                 | VDD = 2.5V, should connect to CLKIN through AC coupling and bias circuit |      | 0.8  |      | V      |

**VDD = 3.3V \pm5%**; for **5PB1213 / 1214 / 1216**, ambient Temperature -40° to +105°C, unless stated otherwise

| Parameter                                                  | Symbol                            | Conditions                                                               | Min. | Тур. | Max. | Units  |

|------------------------------------------------------------|-----------------------------------|--------------------------------------------------------------------------|------|------|------|--------|

| Input Frequency                                            |                                   |                                                                          | 0    |      | 200  | MHz    |

| Output Rise Time                                           | t <sub>OR</sub>                   | 0.66 to 2.64V, C <sub>L</sub> = 5pF                                      |      | 0.6  | 1.0  | ns     |

| Output Fall Time                                           | t <sub>OF</sub>                   | 2.64 to 0.66V, C <sub>L</sub> = 5pF                                      |      | 0.6  | 1.0  | ns     |

| Propagation Delay                                          | Note 1                            | Note 1                                                                   | 1.4  | 1.9  | 2.4  | ns     |

| Buffer Additive Phase Jitter, RMS                          |                                   | 26MHz TCXO clipped sine wave input,<br>Integration Range: 12kHz to 20MHz |      | 377  |      | fs     |

|                                                            |                                   | 125MHz LVCMOS input,<br>Integration Range: 12kHz to 20MHz                |      | 18   |      | fs     |

| Output to Output Skew                                      | t <sub>SKEWO-O</sub>              | Note 2, Rising edges at VDD/2                                            |      | 20   | 50   | ps     |

| Device to Device Skew                                      | t <sub>SKEWD-D</sub>              | Rising edges at VDD/2                                                    |      |      | 200  | ps     |

| Delay for Output Enable / Disable<br>Time ENABLEx to BCLKn | t <sub>EN</sub> /t <sub>DIS</sub> | CL < 5pF                                                                 |      |      | 3    | cycles |

| Start-up Time                                              | t <sub>START-UP</sub>             | Part start-up time for valid outputs after VDD ramp-up                   |      |      | 2    | ms     |

| TCXO Clock Clipped Sine Wave Input Voltage Swing Level     | VIN <sub>pp</sub>                 | VDD = 3.3V, should connect to CLKIN through AC coupling and bias circuit |      | 0.5  |      | V      |

#### Notes:

- With rail to rail input clock.

Between any 2 outputs with equal loading.

Duty cycle on outputs will match incoming clock duty cycle. Consult IDT for tight duty cycle clock generators.

### **Test Load and Circuit**

7

## **AC Coupling and Bias Circuit**

| Component | Value |

|-----------|-------|

| C1        | 1µF   |

| R1        | 10k   |

| R2        | 10k   |

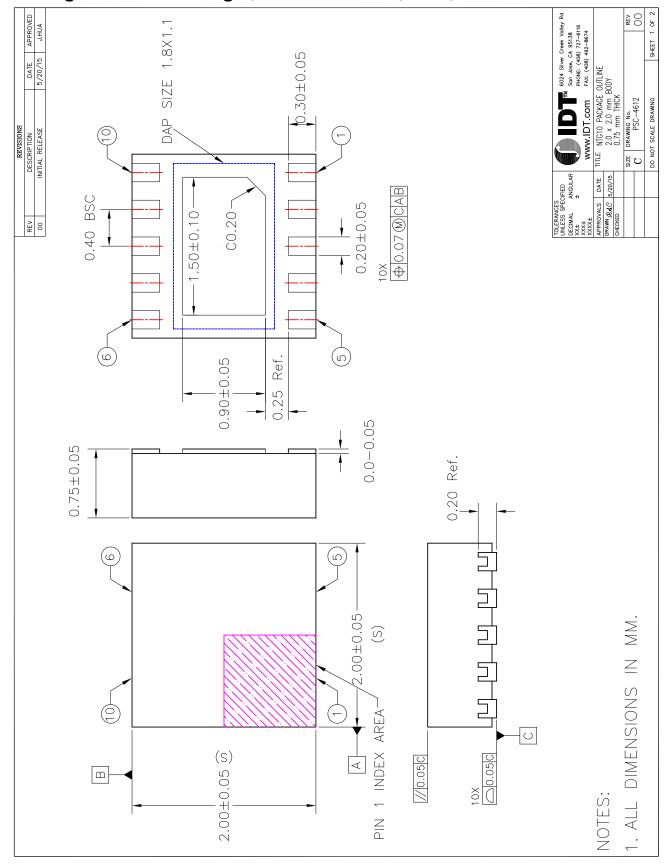

## Package Outline Drawings (5PB1203 / 5PB1213 10-pin DFN)

## Package Outline Drawings (5PB1203 / 5PB1213 10-pin DFN), cont.

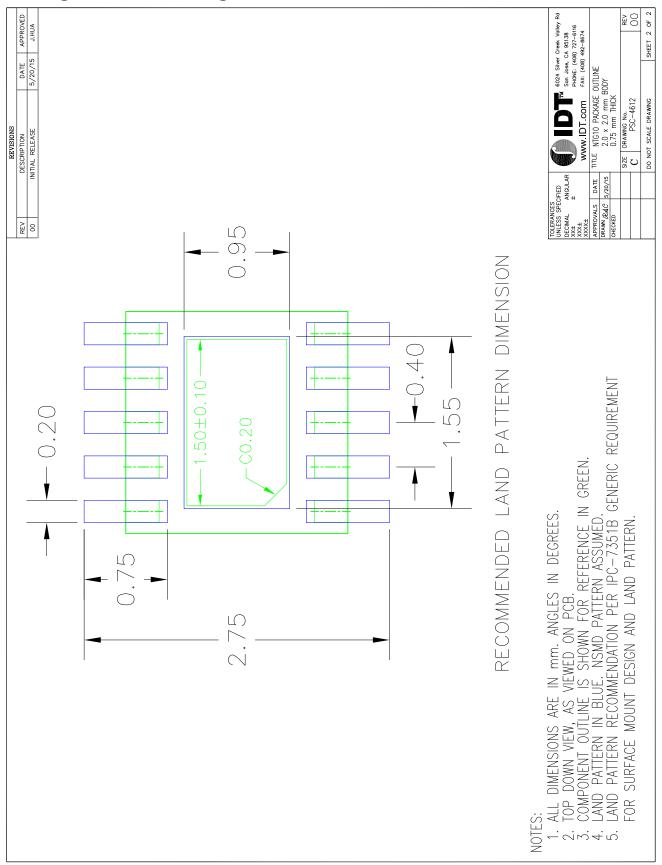

# Package Outline Drawings (5PB1204 / 5PB1214 16-pin VFQFPN)

# Package Outline Drawings (5PB1204 / 5PB1214 16-pin VFQFPN), cont.

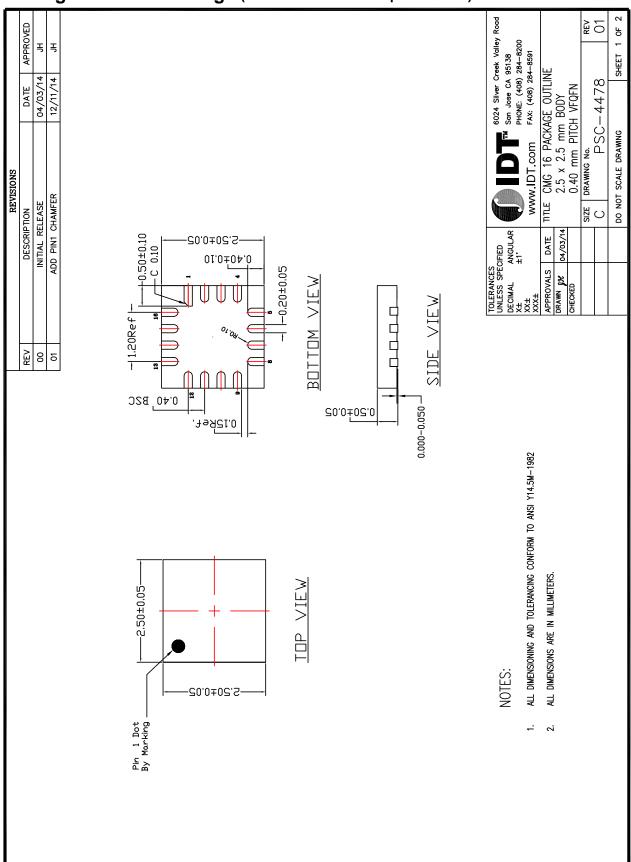

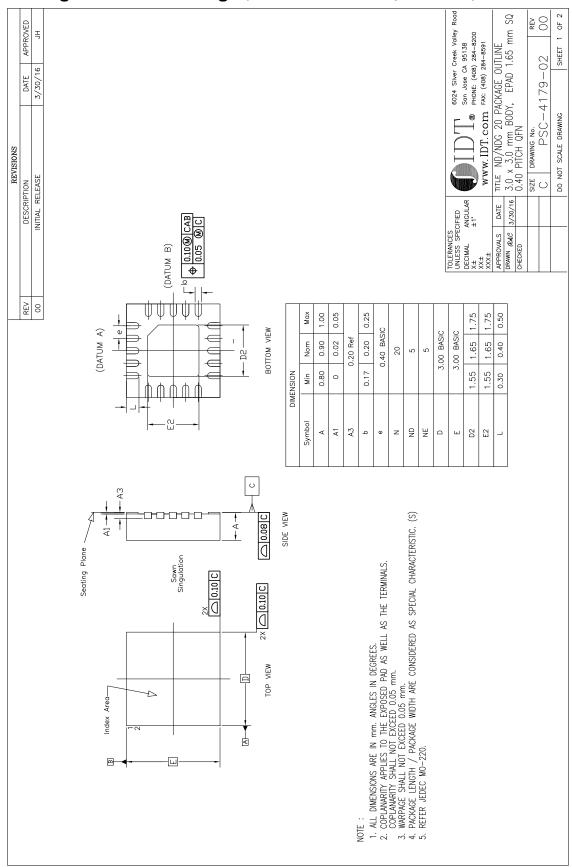

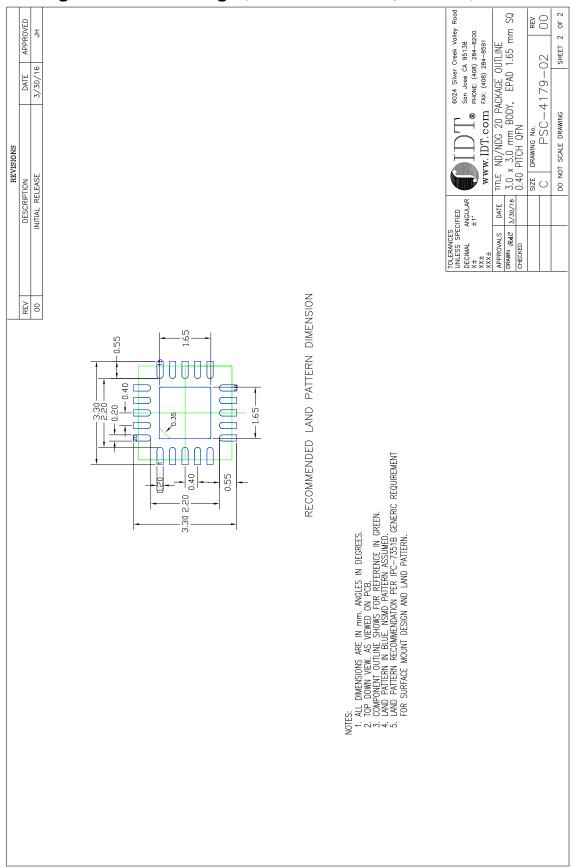

# Package Outline Drawings (5PB1206 / 5PB1216 20-pin VFQFPN)

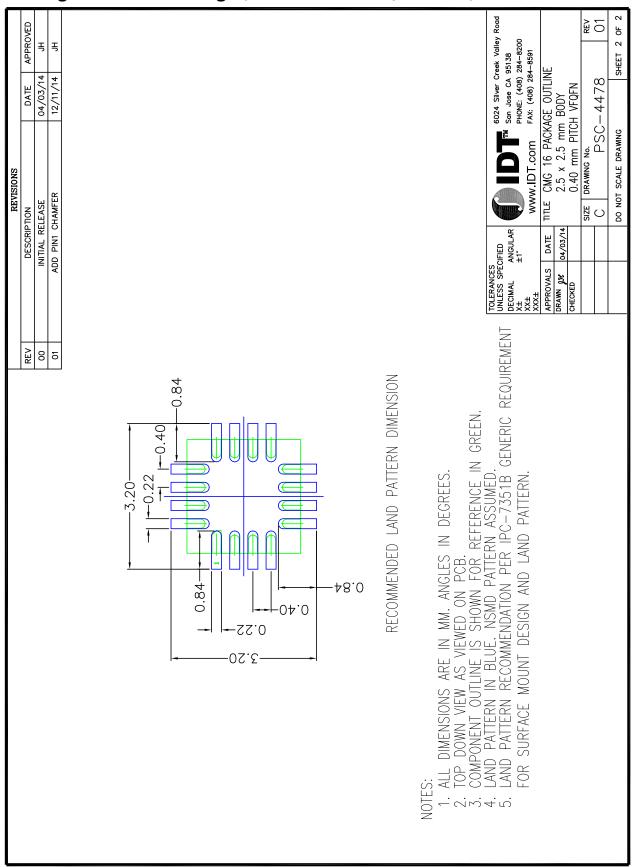

# Package Outline Drawings (5PB1206 / 5PB1216 20-pin VFQFPN), cont.

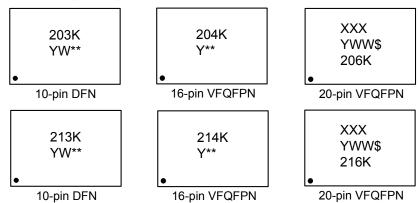

## **Ordering Information**

| Part / Order Number | Shipping Packaging | Package       | Temperature   |

|---------------------|--------------------|---------------|---------------|

| 5PB1203NTGK         | Cut Tape           | 10-pin DFN    | -40 to +105°C |

| 5PB1203NTGK8        | Tape and Reel      | 10-pin DFN    | -40 to +105°C |

| 5PB1213NTGK         | Cut Tape           | 10-pin DFN    | -40 to +105°C |

| 5PB1213NTGK8        | Tape and Reel      | 10-pin DFN    | -40 to +105°C |

| 5PB1204CMGK         | Cut Tape           | 16-pin VFQFPN | -40 to +105°C |

| 5PB1204CMGK8        | Tape and Reel      | 16-pin VFQFPN | -40 to +105°C |

| 5PB1214CMGK         | Cut Tape           | 16-pin VFQFPN | -40 to +105°C |

| 5PB1214CMGK8        | Tape and Reel      | 16-pin VFQFPN | -40 to +105°C |

| 5PB1206NDGK         | Tube               | 20-pin VFQFPN | -40 to +105°C |

| 5PB1206NDGK8        | Tape and Reel      | 20-pin VFQFPN | -40 to +105°C |

| 5PB1216NDGK         | Tube               | 20-pin VFQFPN | -40 to +105°C |

| 5PB1216NDGK8        | Tape and Reel      | 20-pin VFQFPN | -40 to +105°C |

<sup>&</sup>quot;G" after the two-letter package code denotes Pb-Free configuration, RoHS compliant.

## **Marking Diagrams**

### Notes:

- 1. "\*\*" is the lot number.

- 2. "YWW", "YW", or "Y" are the last digit(s) of the year and week that the part was assembled.

- 3. "\$" denotes mark code.

- 4. "K" denotes extended temperature range device.

- 5. "XXX" denotes last three characters of Asm lot.

### **Revision History**

| Date              | Description of Change                                                                                                                                                                                                                                                                                       |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| February 28, 2018 | Updated CLKIN input high and low voltage ratings in DC characterization tables.     Updated Absolute Maximum supply voltage (VDD) from 3.465V to 3.8V.                                                                                                                                                      |

| April 10, 2017    | <ol> <li>Updated Operating Supply Current and Operating Voltage values in DC electrical characteristics tables.</li> <li>Updated Propagation Delay and Output skew values in AC electrical characteristics tables.</li> <li>Updated package outline drawings.</li> <li>Updated legal disclaimer.</li> </ol> |

| July 11, 2016     | Initial release.                                                                                                                                                                                                                                                                                            |

Corporate Headquarters 6024 Silver Creek Valley Road San Jose, CA 95138 USA www.IDT.com Sales

1-800-345-7015 or 408-284-8200 Fax: 408-284-2775

www.IDT.com/go/sales

Tech Support

www.idt.com/go/support

DISCLAIMER Integrated Device Technology, Inc. (IDT) and its affiliated companies (herein referred to as "IDT") reserve the right to modify the products and/or specifications described herein at any time, without notice, at IDT's sole discretion. Performance specifications and operating parameters of the described products are determined in an independent state and are not guaranteed to perform the same way when installed in customer products. The information contained herein is provided without representation or warranty of any kind, whether express or implied, including, but not limited to, the suitability of IDT's products for any particular purpose, an implied warranty of merchantability, or non-infringement of the intellectual property rights of others. This document is presented only as a guide and does not convey any license under intellectual property rights of IDT or any third parties.

IDT's products are not intended for use in applications involving extreme environmental conditions or in life support systems or similar devices where the failure or malfunction of an IDT product can be reasonably expected to significantly affect the health or safety of users. Anyone using an IDT product in such a manner does so at their own risk, absent an express, written agreement by IDT.

Integrated Device Technology, IDT and the IDT logo are trademarks or registered trademarks of IDT and its subsidiaries in the United States and other countries. Other trademarks used herein are the property of IDT or their respective third party owners. For datasheet type definitions and a glossary of common terms, visit <a href="https://www.idt.com/go/glossary">www.idt.com/go/glossary</a>. Integrated Device Technology, Inc.. All rights reserved.