# PM0018 Quick reference manual

## ST7 Flash programming

### Introduction

This quick reference manual is intended for users of ST7 Flash microcontrollers. It is a central source for all device-specific data related to Flash programming for the following documents:

- Flash programming reference manual

- ICC protocol reference manual

The latest document revisions can be obtained on-line at http://www.st.com.

## **Contents**

| 1      | Devi   | ce specific information         | . 3 |

|--------|--------|---------------------------------|-----|

|        | 1.1    | Flash technology types          | 3   |

|        | 1.2    | RC calibration value addresses  | 3   |

|        | 1.3    | Implemented ICC features        | 4   |

|        | 1.4    | System memory addresses         | 7   |

| Append | ix A S | ST7SCR ICC mode entry           | . 8 |

|        | A.1    | ROM product, ICC mode selection | 8   |

| 2      | Revi   | sion history                    | o   |

### 1 Device specific information

### 1.1 Flash technology types

Three Flash technologies are available in the ST7 family with different programming methods. Each ST7 Flash microcontroller is associated with one of these three technologies as shown in *Table 1: ST7 Flash microcontroller types*.

- XFlash (Extended): Flash memory based on a EEPROM technology

- HDFlash (High Density): Flash memory based on Flash technology

- CFlash (ST72Cxxx): Flash memory based on a EEPROM technology (see AN1179 for more details)

For further information on XFlash and HDFlash, refer to the Flash programming reference manual.

Table 1. ST7 Flash microcontroller types

| ST7 Flash families | Flash<br>technology | ST7 devices                                                                        | Programming methods |  |  |

|--------------------|---------------------|------------------------------------------------------------------------------------|---------------------|--|--|

|                    | XFlash              | XFlash ST7FLITEx, ST7FDALI, ST7FLx ST72F26x, ST72F34x                              |                     |  |  |

| ST72Fxxx           | HDFlash             | ICP                                                                                | IAP                 |  |  |

| ST72Cxxx           | CFlash              | ST72C104, ST72C215, ST72C216, ST72C254<br>ST72C124, ST72C314, ST72C334<br>ST72C171 | ISP                 |  |  |

#### 1.2 RC calibration value addresses

Table 2 holds the addresses of the RC calibration values in the event of removal of readout protection. The full procedure of restoring RC calibration values is described in the Flash programming reference manual. This procedure applies only to the devices listed in the following table. For the other devices, the RC calibration values are not lost if the readout protection is removed.

Table 2. List of RC calibration value addresses

| Device           | RCCR0  | RCCR1  |  |  |

|------------------|--------|--------|--|--|

| ST7FLITE0/ST7FL0 | 0xF960 | 0xF961 |  |  |

| ST7FLITE1        | 0xDEE0 | 0xDEE1 |  |  |

| ST7FLITE2        | 0xDEE0 | 0xDEE1 |  |  |

47/

### 1.3 Implemented ICC features

*Table 3* defines the implemented ICC features and their main characteristics for each ST7 device. The data mentioned in this table is described in detail in the ICC protocol reference manual.

#### Description of legends for Table 3

**ICC monitor**: Three different ICC monitors can be implemented: basic (for ST7 with HDFlash and small XFlash), medium (for ST7 ROM) and advanced (for ST7 XFlash with debug module). Refer to the ICC protocol reference manual for more details.

**ICC mode entry**: Different methods exists for entering ICC mode. Refer to the ICC protocol reference manual for more details.

IAP:IAP is not available on 4K HDFlash versions.

**ICD**: ICD can be managed with or without a debug module, refer to the ICC protocol reference manual for more details

**DM**: The Debug Module (DM) is an ST7 hardware peripheral able to manage instruction stepping, complex breakpoints and abort for ICD development tools. The ST72F325, ST7FSuperlite, ST7FLite2 and ST7FHUB Debug Modules do not feature the WP bit capability and the register protection when MTR=0. Refer to the ICC protocol reference manual for more details.

**Ext clock**: If this number of pulses is generated, the ST7 does not take into account the option byte configuration stored in the Flash memory, and an external clock has to be provided. In this case, the microcontroller configuration corresponds to the factory default option byte values, see product datasheet for more details. Note that in this mode, reserved Flash locations (which may contain internal oscillator calibration data for example) are not write protected, and could be corrupted if you program the device using a wrong address.

#### Caution:

To know on which pin the external clock must be provided please refer to the section related to the ICC interface in the product datasheet.

**Appli clock**: If this number of pulses is generated, the ST7 takes into account the option byte configuration (except the watchdog which is always software in this condition). In this case, be sure that the selected clock source is available in the application (see product datasheet for more details).

Note that in this mode, reserved Flash locations are write protected, so this mode is safer than external clock mode.

Table 3. Implemented ICC features in ST7 devices

|                                                           | ICC<br>monitor | Embedded ICC applications |     |     |     | 3  | ICC mode entry                |                               |         |                    |                    |

|-----------------------------------------------------------|----------------|---------------------------|-----|-----|-----|----|-------------------------------|-------------------------------|---------|--------------------|--------------------|

|                                                           |                |                           |     |     |     |    |                               | Pulse                         |         |                    |                    |

| Devices                                                   |                |                           |     |     | ICD |    | Window                        | Pulse                         |         | Number             |                    |

|                                                           |                | ICP                       | IAP | ICT |     | DM | type                          | counter<br>reset pin          | Pin     | Ext.<br>clock      | Appli<br>clock     |

| ST7FLITE0/ST7FL0,<br>ST7FLITES2/S5 <sup>(1)</sup>         | basic          | Х                         | Х   | Х   | Х   |    |                               |                               |         |                    | 38                 |

| ST7FLITE2/1/ST7DALI                                       | advanced       | Х                         | Х   | Х   | Χ   | 1  |                               |                               | ICCDATA | 35                 |                    |

| ST7FLITE4M/3/1B,<br>ST7FL3/1B                             | advanced       | х                         | Х   | Х   | Х   | 1  |                               | ICCCLK (2)                    |         |                    | 38 <sup>(3)</sup>  |

| ST7FLITEUS <sup>(4)</sup> ,<br>ST7LITEU0                  | advanced       | Х                         | х   | Х   | х   | 1  |                               |                               |         |                    | 38 <sup>(5)</sup>  |

| ST72F34x <sup>(6)</sup>                                   | advanced       | Х                         | Х   | Х   | Х   | 1  | -                             |                               |         |                    | 38                 |

| ST72F26x                                                  | advanced       | Х                         | Х   | Х   | Х   |    | -                             |                               |         |                    | 38 (8)             |

| ST7226x <sup>(9)</sup>                                    | medium         |                           |     | Х   |     |    | Controlled                    | ICCSEL (7)                    |         |                    | 38                 |

| ST72F561/F361                                             | basic          | Х                         | Х   | Х   | Х   |    | Controlled                    |                               |         |                    | 36                 |

| ST7FHUB                                                   | basic          | Х                         | Х   | Х   | Х   | 1  |                               |                               |         | 3                  | 88 <sup>(10)</sup> |

| ST72F325/F321B                                            | basic          | Х                         | Х   | Х   |     | 1  |                               |                               |         | 36                 |                    |

| ST72F321/F521<br>ST72F324BJ6/K6                           | basic          | х                         | х   | Х   |     |    |                               |                               |         |                    | 39                 |

| ST7232x/521 <sup>(9)</sup><br>(incl. L and B versions)    | medium         |                           |     | Х   |     |    |                               |                               |         |                    |                    |

| ST72F32A<br>ST72F324L<br>ST72F324BJ2/J2<br>ST72F324BK4/K4 | basic          | Х                         | x   | Х   |     |    |                               |                               |         |                    | Not<br>supported   |

| ST72F60x/F62x/F63x/<br>F63Bx/ST7FSCR                      | basic          | х                         | х   | Х   |     |    |                               | Not<br>applicable             | ICCSEL  | 38 <sup>(10)</sup> |                    |

| ST72F651 <sup>(1)</sup>                                   | basic          | Х                         | Х   | Х   |     |    | Fixed<br>256.t <sub>CPU</sub> |                               |         |                    |                    |

| ST7260/61x/62x/63x/<br>63Bx/65/ ST7SCR <sup>(9)</sup>     | medium         |                           |     | Х   |     |    |                               |                               |         |                    |                    |

| ST7FMC                                                    | basic          | Х                         | Х   | Х   | Х   | 1  | Controlled                    | VPP/<br>ICCSEL <sup>(7)</sup> | ICCDATA | (                  | 38 <sup>(11)</sup> |

For these devices, the ST7 has to enter external clock mode in order to be able to reprogram devices with hardware watchdog enabled. Refer to the External Clock/Application Clock ICC modes section of the ICC protocol reference manual for more details.

57

<sup>2.</sup> The pulse counter is reset when  $\overline{\text{RESET}}$  is low and ICCCLK is high.

<sup>3.</sup> In 38-pulse ICC mode, the internal RC oscillator is forced as a clock source, regardless of the selection in the option byte.

- In the ST7FLITEUS, an interrupt is generated in ICC mode due to ICCCLK on PA1, configured as pull-up interrupt by default. The workaround is to enable the interrupt mask before the IRET of the ICC monitor, when executing the GO command

- 5. Contrary to the behavior described in "appli clock" legend, the ST7FLITEUS takes into account the option byte configuration including the hardware watchdog if it is enabled. Consequently, 35-pulse mode must be used if hardware watchdog is enabled.

- watchtog is enabled.

In addition, when ST7FLITEUS is used in 38-pulse mode, the internal 8 MHz RC is selected as clock source if option CKSEL[1:0]=00h, otherwise, if CKSEL is not 00h, AWU RC is selected as clock source. External clock can not be selected when using 38-pulse mode.

- when using 38-pulse mode.

Limitation: In ST7FLITEUS when programming the LVD option from OFF to ON in 38-pulse mode and if the AVD is OFF, a spurious reset is generated and ICC communication is lost. The workaround is either to use 35-pulse mode or to ensure that the programming tool generates a reset after programming the Option Byte.

- 6. There are 4 option bytes in this device: Option byte 0 and 1 starting at address E000h and Option byte 2 and 3 starting at C000h. Take care to program Option byte 0, 1, 2 and 3 in the same routine. Then the following steps must be followed to modify the option bytes:

- -Read the 4 bytes in the device

- -Modify as desired

- -Write the 4 bytes in the device

- 7. The pulse counter is reset when RESET and ICCSEL are both low.

- 8. If ICC mode is entered using this pulse sequence, the clock source option bits must not be modified during the ICC session. To modify the clock source option bits, use the "external clock" pulse sequence.

- All ROM devices support the medium variant of the ICC monitor. Hence these devices can be read if the Read-out protection has not been enabled. However it must be noted that only the program memory of these devices can be read but not the option bytes.

- 10. For these devices, if this number of pulses is generated, the ST7 can be supplied by an external clock source or a resonator. In this case, legends on "ext clock" and "applil clock" are not relevant.

- 11. For these devices, if this number of pulses is generated, the ST7 will be supplied by its internal clock. No external clock is required in ICC mode.

## 1.4 System memory addresses

In certain products, the System memory is accessible either in USER or ICC modes. Its address is given in *Table 4* below.

Table 4. System memory addresses

| Product                    |                   | System memory addresses |                  |               |                  |  |  |  |

|----------------------------|-------------------|-------------------------|------------------|---------------|------------------|--|--|--|

| Name                       | Identifier<br>(1) | ICC_mode                | ICC_monitor_trap | ICC_send_byte | ICC_receive_byte |  |  |  |

| ST7FLITE0/S2/S5/<br>ST7FL0 | 819 1             | F98Bh                   | F98Fh            | NA            | F9A6h            |  |  |  |

| ST7FLITE1B<br>ST7FL1B      | 829 1             | EF2Bh                   | EF2Fh            | EF00h         | EF6Bh            |  |  |  |

| ST7FLITE2/1/FDALI          | 837 1             | DF2Bh                   | DF2Fh            | DF00h         | DF6Bh            |  |  |  |

| ST7FLITE3/ST7FL3           | 852 0             | DF2Bh                   | DF2Fh            | DF00h         | DF6Bh            |  |  |  |

| STFLITE4M                  | 878 0             | DF2Bh                   | DF2Fh            | DF00h         | DF6Bh            |  |  |  |

| ST7FLITEUS                 | 875 0             | DF2Bh                   | DF2Fh            | DF00h         | DF6Bh            |  |  |  |

| ST7FLITEU0                 | 876 0             | DF2Bh                   | DF2Fh            | DF00h         | DF6Bh            |  |  |  |

| ST72F26X                   | 825 1             | DF2Bh                   | DF2Fh            | DF00h         | DF6Bh            |  |  |  |

| ST7226X                    | 826 1             | DF29h                   | DF2Dh            | DF00h         | DF47h            |  |  |  |

| ST72F34X                   | 864 1             | BF2Bh                   | BF2Fh            | BF00h         | BF6Bh            |  |  |  |

<sup>1.</sup> For more details, refer to the ICC protocol reference manual.

**47/**

### Appendix A ST7SCR ICC mode entry

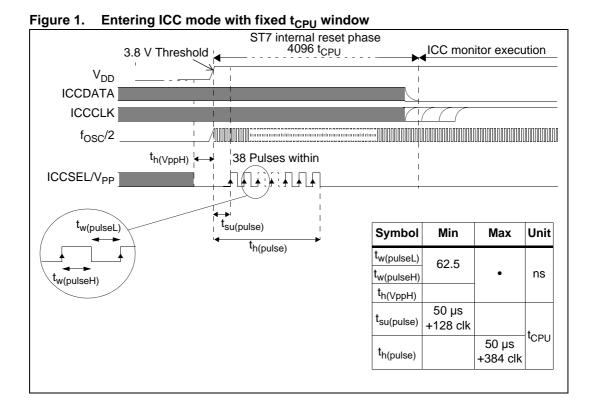

For an external controller to be able to put the ST7SCR into  $\underline{\sf ICC}$  mode, the procedure has to be slightly modified because the ST7SCR has no external  $\overline{\sf RESET}$  pin to synchronize the start of the pulse train that defines  $\underline{\sf ICC}$  mode entry. Instead the synchronization has to be done on the  $V_{\mathsf{IT+}}$  rising threshold at power on. This can be implemented by a external analog comparator with a threshold of 3.8V.

As shown in Figure 1, a startup delay has to be inserted, specified as follows:

$t_{STARTUP}$  min. 50  $\mu$ s +128  $t_{CPU}$   $t_{STARTUP}$  max. 50  $\mu$ s +384  $t_{CPU}$

A.1 ROM product, ICC mode selection

In ROM ST7SCR devices, the  $V_{PP}$  pin is replaced by a pin called TM (for Test mode). When this pin is high, the LVD is powered off, pin PA6 becomes a reset pin and pin PA0 becomes the  $V_{PP}$  pin.

To enter ICC mode:

- 1. Hold the TM pin at high level.

- 2. Reset the chip by applying a low level pulse on PA6

- 3. Apply 38 pulses on the PA0 pin as shown in Figure 1.

- 4. When the mode entry window is finished, the PA0 port acts as the ICCDATA function.

# 2 Revision history

Table 5. Document revision history

| Date         | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|--------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 02-May-2005  | 1        | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| 16-Dec-2005  | 2        | Added information for ST72F325, ST72F361, ST7FLITE1B                                                                                                                                                                                                                                                                                                                                                                    |  |

| 15-Fev-2006  | 3        | Added information in <i>Table 3</i> . for ST72F32A, ST7FL0,ST7FL3 Modified notes 6 and 7 <i>on page 6</i>                                                                                                                                                                                                                                                                                                               |  |

| 17-July-2006 | 4        | Added information in <i>Table 1</i> . and <i>Table 3</i> . for ST72F60, ST7263B, ST72F33B, ST72F34x, ST7FLITEUS                                                                                                                                                                                                                                                                                                         |  |

| 23-Mar-2007  | 5        | Modified text in <i>Chapter 1.2: RC calibration value addresses</i> ST7LITEU0 added in <i>Table 3.</i> and <i>Table 4.</i> Added note 11 to <i>Table 3.</i> Changed orders of the notes. Modified ST72F34x in <i>Table 3.</i> (ICCSEL instead of ICCCLK)                                                                                                                                                                |  |

| 11-May-2007  | 6        | STFLITE4M added to <i>Table 3: Implemented ICC features in ST7 devices</i> and <i>Table 4: System memory addresses.</i> Other changes in <i>Table 3:</i> – information on ST72F32x devices modified,  – one Note removed and <i>Note 3</i> added,  – 39 application clock pulses not supported on ST72F32A,  – Notes on legends in <i>Table 3.</i> replaced by a section: "description of legends for <i>Table 3.</i> " |  |

**577**

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2007 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com