**BOARD ROUTING RECOMMENDATIONS**

#### **TABLE OF CONTENTS**

| 4 |     | ^ | 000 | -  | _ |

|---|-----|---|-----|----|---|

| 1 | l ( |   | SCO | או | - |

#### 2.0 PC BOARD REQUIREMENTS

- 2.1 MATERIAL THICKNESS

- 2.2 HOLE DIMENSIONS

- 2.3 LAYOUT

#### 3.0 HIGHSPEED ROUTING

- 3.1 GENERAL ROUTING EXAMPLE

- 3.2 HIGH SPEED REFERENCE PLANE ANTI-PAD

- 3.3 CONNECTOR THROUGH-HOLE INTERFACE VIA STUBS

- 3.4 SKEW COMPENSATION

- 3.5 TRACE COMPARISON FOR DIFFERENTIAL SIGNALING

| REVISION:        | ECN INFORMATION:         | TITLE:                                                              |                  |          | SHEET No.            |

|------------------|--------------------------|---------------------------------------------------------------------|------------------|----------|----------------------|

| В                | EC No: <b>S2014-1130</b> | SI Routing Guidelines for DDR4 DIMM Vertical Through-Hole Connector |                  |          | <b>1</b> of <b>7</b> |

|                  | DATE: 2014/05/19         |                                                                     | 1017             |          |                      |

| DOCUMENT NUMBER: |                          | CREATED / REVISED BY:                                               | CHECKED BY:      | APPRO\   | <u>/ED BY:</u>       |

| AS-78726-002     |                          | CMWONG 2014/05/19                                                   | CHYEO 2014/05/19 | WTCHUA 2 | 2014/05/19           |

# molex®

## **DDR4 DIMM THROUGH-HOLE CONNECTOR**

**BOARD ROUTING RECOMMENDATIONS**

#### 1.0 SCOPE

This specification covers the high-speed PCB routing recommendations of DQ and DQS signals for 78726 (Standard) and 151016 (Aero) series connector. The connector is a vertical throughhole type designed for use with 0.66mm finished vias. The pins of the connector are soldered for mechanical retention to the PC board.

**DISCLAIMER:** Molex does not guarantee the performance of the final product to match the information provided in this document. All information in this report is considered proprietary, confidential and the property of Molex. This guide is not intended as a substitute for engineering analysis.

FIGURE 1

| REVISION:        | ECN INFORMATION:          | TITLE:                |                                                    |          | SHEET No.            |

|------------------|---------------------------|-----------------------|----------------------------------------------------|----------|----------------------|

| В                | EC No: <b>\$2014-1130</b> |                       | Routing Guidelines for<br>/ertical Through-Hole Co | nnector  | <b>2</b> of <b>7</b> |

|                  | DATE: <b>2014/05/19</b>   |                       | 2017                                               |          |                      |

| DOCUMENT NUMBER: |                           | CREATED / REVISED BY: | CHECKED BY:                                        | APPRO\   | /ED BY:              |

| AS-78726-002     |                           | CMWONG 2014/05/19     | CHYEO 2014/05/19                                   | WTCHUA 2 | 2014/05/19           |

# molex®

### DDR4 DIMM THROUGH-HOLE CONNECTOR

#### **BOARD ROUTING RECOMMENDATIONS**

#### 2.0 PC BOARD REQUIREMENTS

#### 2.1 MATERIAL THICKNESS

The recommended PC board thickness shall be 1.57mm, 2.36mm or 3.00mm, depending on the length of the lead-in tail of the terminal selected. Suitable PC board material shall be glass epoxy (FR-4).

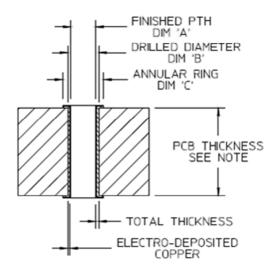

#### 2.2 HOLE DIMENSIONS

The holes for the connector assembly must be drilled and plated through to dimensions specified in Figure 2.

#### Recommended Hole Dimensions

| DIM. "A"                    | DIM. "B"                      | DIM. "C"                      |

|-----------------------------|-------------------------------|-------------------------------|

| MM (INCH)                   | MM (INCH)                     | MM (INCH)                     |

| 0.66+/-0.05 (0.026+/-0.002) | 0.762+/-0.01 (0.030+/-0.0004) | 0.9652+/-0.05 (0.038+/-0.002) |

Note: Refer to appropriate sales drawing for recommended PCB holes and PCB thickness

#### FIGURE 2

#### 2.3 LAYOUT

The holes for the connector assembly must be precisely located to ensure proper placement and optimum performance of the connector assembly. Refer to the applicable Sales Drawing for the recommended hole pattern, dimensions and tolerances.

| REVISION:        | ECN INFORMATION:         | TITLE:                |                                                                     |                | SHEET No.     |  |

|------------------|--------------------------|-----------------------|---------------------------------------------------------------------|----------------|---------------|--|

| В                | EC No: <b>S2014-1130</b> |                       | SI Routing Guidelines for DDR4 DIMM Vertical Through-Hole Connector |                |               |  |

|                  | DATE: 2014/05/19         |                       | <b>3</b> of <b>7</b>                                                |                |               |  |

| DOCUMENT NUMBER: |                          | CREATED / REVISED BY: | CHECKED BY:                                                         | <u>APPRO</u> V | <u>ED BY:</u> |  |

| AS-78726-002     |                          | CMWONG 2014/05/19     | CHYEO 2014/05/19                                                    | WTCHUA 2       | 2014/05/19    |  |

## molex®

## **DDR4 DIMM THROUGH-HOLE CONNECTOR**

**BOARD ROUTING RECOMMENDATIONS**

#### 3.0 HIGH-SPEED ROUTING

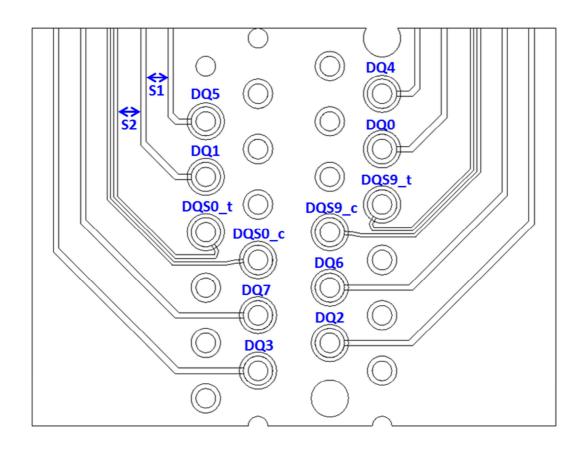

#### 3.1 GENERAL ROUTING EXAMPLE (other configurations are possible)

The routing example shown is for reference only. The above was extracted to show a portion that contains the routing of DQ and DQS signals. It shows 2 layers overlaid (1 signal and 1 reference ground layer).

| Parameter                          | MM (INCH)                         |

|------------------------------------|-----------------------------------|

| Single-ended trace width           | 0.1651 (0.0065)                   |

| Differential trace width / spacing | 0.1016 (0.0040) / 0.1016 (0.0040) |

| DQ to DQ spacing (S1)              | 0.6604 (0.0260)                   |

| DQ to DQS spacing (S2)             | 0.6604 (0.0260)                   |

Note: All the parameters above can vary from recommendation to meet board thickness, routing and electrical requirements.

| REVISION:        | ECN INFORMATION:         | TITLE:                | Routing Guidelines for |          | SHEET No.     |

|------------------|--------------------------|-----------------------|------------------------|----------|---------------|

| В                | EC No: <b>S2014-1130</b> | DDR4 DIMM V           | <b>4</b> of <b>7</b>   |          |               |

|                  | DATE: <b>2014/05/19</b>  |                       |                        |          | <b>4</b> 01 1 |

| DOCUMENT NUMBER: |                          | CREATED / REVISED BY: | CHECKED BY:            | APPRO\   | /ED BY:       |

| AS-78726-002     |                          | CMWONG 2014/05/19     | CHYEO 2014/05/19       | WTCHUA 2 | 2014/05/19    |

**BOARD ROUTING RECOMMENDATIONS**

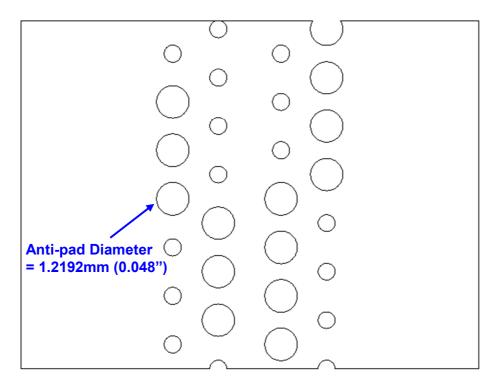

#### 3.2 HIGH-SPEED REFERENCE PLANE ANTI-PAD

#### **All Ground Planes**

Note: Dimensions can vary from recommendation to meet board thickness, routing and electrical requirements.

| REVISION:        | ECN INFORMATION:         | TITLE:                |                      |               | SHEET No.      |

|------------------|--------------------------|-----------------------|----------------------|---------------|----------------|

| В                | EC No: <b>S2014-1130</b> | SI F<br>DDR4 DIMM V   | <b>5</b> of <b>7</b> |               |                |

|                  | DATE: <b>2014/05/19</b>  |                       |                      |               |                |

| DOCUMENT NUMBER: |                          | CREATED / REVISED BY: | CHECKED BY:          | <u>APPROV</u> | <u>/ED BY:</u> |

| AS-78726-002     |                          | CMWONG 2014/05/19     | CHYEO 2014/05/19     | WTCHUA 2      | 2014/05/19     |

**BOARD ROUTING RECOMMENDATIONS**

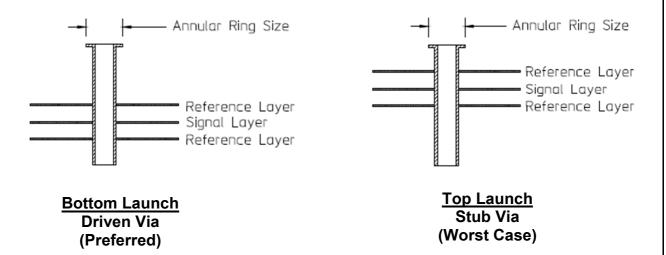

#### 3.3 CONNECTOR THROUGH-HOLE INTERFACE VIA STUBS

Only the signal reference ground planes were shown above and only two annular rings are required for retention of the through-hole via within the printed circuit board. Non-functional annular rings should be removed for unassociated signal layers.

For the connector through-hole vias, specify not only the 0.66mm (0.026") finished hole size but also the 0.762mm (0.030") drill size for the board fabrication.

| REVISION:                               | ECN INFORMATION:                                  | TITLE:                |                      |          | SHEET No.  |

|-----------------------------------------|---------------------------------------------------|-----------------------|----------------------|----------|------------|

| В                                       | EC No: <b>\$2014-1130</b> DATE: <b>2014/05/19</b> | SI F<br>DDR4 DIMM V   | <b>6</b> of <b>7</b> |          |            |

| DOCUMENT NUMBER:                        |                                                   | CREATED / REVISED BY: | CHECKED BY:          | APPRO\   | /ED BY:    |

| AS-78726-002                            |                                                   | CMWONG 2014/05/19     | CHYEO 2014/05/19     | WTCHUA 2 | 2014/05/19 |

| TEMPLATE FILENAME: SPM[SIZE_A](V.1).DOC |                                                   |                       |                      |          |            |

**BOARD ROUTING RECOMMENDATIONS**

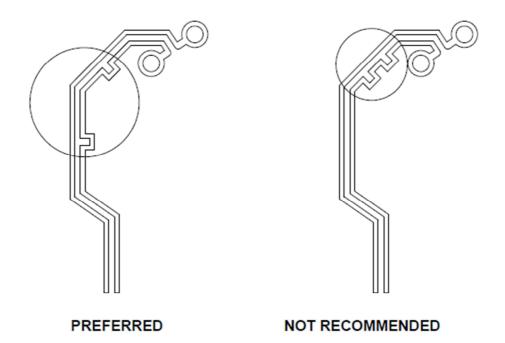

#### 3.4 SKEW COMPENSATION

It is recommended that skew compensation be distributed verses grouped in one or more locations. This applies for both intra skew compensation of each DQS pair and inter skew compensation between all DQ and DQS within the same data lane group.

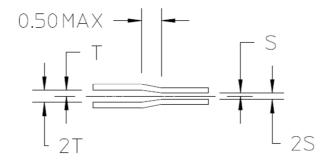

#### 3.5 TRACE COMPARISON FOR DIFFERENTIAL SIGNALING

TRANSITION SHOULD BE SYMMETRIC

| REVISION:        | ECN INFORMATION:         | TITLE:                                                                 |                  |          | SHEET No.            |

|------------------|--------------------------|------------------------------------------------------------------------|------------------|----------|----------------------|

| В                | EC No: <b>S2014-1130</b> | SI Routing Guidelines for<br>DDR4 DIMM Vertical Through-Hole Connector |                  |          | <b>7</b> of <b>7</b> |

|                  | DATE: <b>2014/05/19</b>  |                                                                        | 7 01 7           |          |                      |

| DOCUMENT NUMBER: |                          | CREATED / REVISED BY:                                                  | CHECKED BY:      | APPRO\   | /ED BY:              |

| AS-78726-002     |                          | CMWONG 2014/05/19                                                      | CHYEO 2014/05/19 | WTCHUA 2 | 2014/05/19           |