# **UBA2037**

# Full bridge control IC for HID general lighting

Rev. 01 — 30 October 2008

Product data sheet

## 1. General description

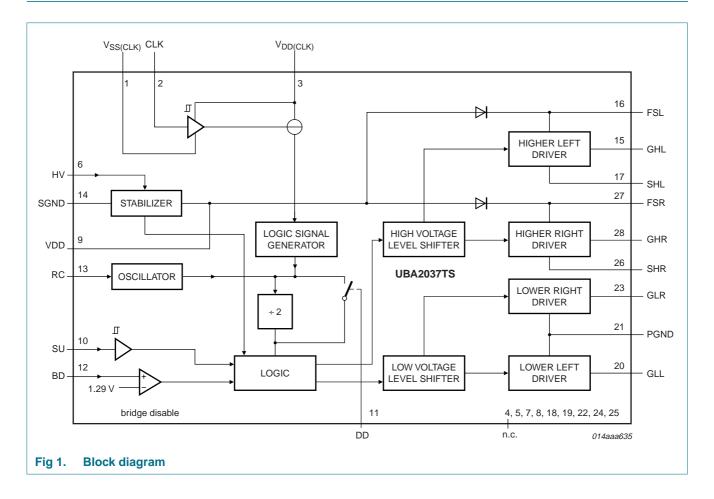

The UBA2037 is a high voltage monolithic Integrated Circuit (IC) manufactured in a High Voltage Silicon On Insulator (HVSOI) process. This circuit is designed for driving MOSFETs in a full bridge configuration. In addition, it features a disable function, an internal adjustable oscillator and an external clock input function with a high-voltage level shifter for driving the bridge. To guarantee an accurate 50 % duty cycle, the oscillator signal can be passed through a divider before being fed to the output drivers.

The UBA2037 is especially suitable for High Intensity Discharge (HID) lamp drivers for projectors and general lighting applications.

#### 2. Features

- Full bridge driver circuit

- Integrated bootstrap diodes

- 464 V integrated high voltage level shift function to drive HID lamps below ground level

- 550 V series regulator input to make the internal supply

- 550 V maximum bridge voltage

- Accurate bridge disable function

- Input for start-up delay

- Adjustable oscillator frequency

- Selectable frequency divider

- Predefined bridge position during start-up

- Adaptive non-overlap

# 3. Applications

- The UBA2037 can drive (via the power MOSFETs) any kind of load in a full bridge configuration.

- The circuit is especially designed as a commutator controller for HID lamps in projectors and general lighting applications.

# Full bridge control IC for HID general lighting

# 4. Ordering information

Table 1. Ordering information

| Type number | Package |                                                                   |          |

|-------------|---------|-------------------------------------------------------------------|----------|

|             | Name    | Description                                                       | Version  |

| UBA2037T    | SO24    | plastic small outline package; 24 leads; body width 7.5 mm        | SOT137-1 |

| UBA2037TS   | SSOP28  | plastic shrink small outline package; 28 leads; body width 5.3 mm | SOT341-1 |

# 5. Block diagram

# Full bridge control IC for HID general lighting

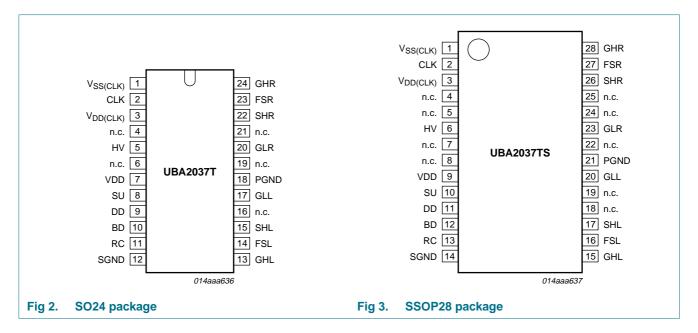

# 6. Pinning information

## 6.1 Pinning

## 6.2 Pin description

Table 2. Pin description

| Symbol               | Pin<br>UBA2037T | Pin<br>UBA2037TS | Description                                             |

|----------------------|-----------------|------------------|---------------------------------------------------------|

| V <sub>SS(CLK)</sub> | 1               | 1                | negative supply voltage for logic oscillator input      |

| CLK                  | 2               | 2                | oscillator input                                        |

| $V_{\text{DD(CLK)}}$ | 3               | 3                | positive supply voltage for logic oscillator input      |

| n.c.                 | 4               | 4                | not connected                                           |

| n.c.                 |                 | 5                | not connected                                           |

| HV                   | 5               | 6                | high voltage supply input for internal series regulator |

| n.c.                 | 6               | 7                | not connected                                           |

| n.c.                 |                 | 8                | not connected                                           |

| VDD                  | 7               | 9                | internal low voltage supply                             |

| SU                   | 8               | 10               | input for start-up delay                                |

| DD                   | 9               | 11               | input for divider disable                               |

| BD                   | 10              | 12               | input for bridge disable                                |

| RC                   | 11              | 13               | RC input for internal oscillator                        |

| SGND                 | 12              | 14               | signal ground                                           |

| GHL                  | 13              | 15               | gate driver output for upper left MOSFET                |

| FSL                  | 14              | 16               | floating supply left                                    |

| SHL                  | 15              | 17               | source upper left MOSFET                                |

| n.c.                 | 16              | 18               | not connected                                           |

#### Full bridge control IC for HID general lighting

Table 2. Pin description ... continued

| Symbol | Pin<br>UBA2037T | Pin<br>UBA2037TS | Description                               |

|--------|-----------------|------------------|-------------------------------------------|

| n.c.   |                 | 19               | not connected                             |

| GLL    | 17              | 20               | gate driver output for lower left MOSFET  |

| PGND   | 18              | 21               | power ground                              |

| n.c.   | 19              | 22               | not connected                             |

| GLR    | 20              | 23               | gate driver output for lower right MOSFET |

| n.c.   | 21              | 24               | not connected                             |

| n.c.   |                 | 25               | not connected                             |

| SHR    | 22              | 26               | source upper right MOSFET                 |

| FSR    | 23              | 27               | floating supply right                     |

| GHR    | 24              | 28               | gate driver upper right MOSFET            |

## 7. Functional description

### 7.1 Supply voltage

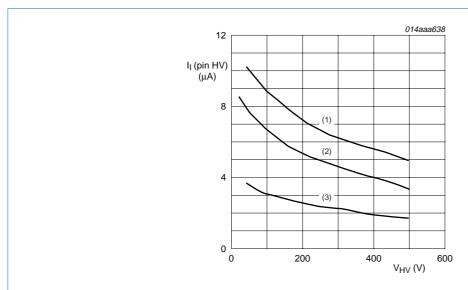

The UBA2037 is powered by a supply voltage applied to pin HV, e.g. the supply voltage of the full bridge. The IC generates its own low supply voltage for its internal circuitry. Therefore an additional low voltage supply is not required. A capacitor has to be connected to pin VDD to obtain a ripple-free internal supply voltage. The circuit can also be powered by a low voltage supply directly applied to pin VDD. In this case pin HV should be connected to pin VDD or pin SGND. The maximum current that the internal series regulator can deliver, is temperature dependent. This is shown in Figure 4.

### 7.2 Start-up

With an increasing supply voltage the IC enters the start-up state i.e. the upper power transistors are set in off-state and the lower power transistors are switched on. During the start-up state the bootstrap capacitors are charged. The start-up state is defined until  $V_{VDD} = V_{startup(VDD)}$  or  $V_{HV} = V_{startup(HV)}$ . The state of the outputs during the start-up phase is overruled by the bridge disable function.

### 7.3 Oscillation state

At the moment the supply voltage on pin VDD exceeds  $V_{startup(VDD)}$  or the supply voltage on pin  $V_{HV}$  exceeds  $V_{startup(HV)}$ , the output voltage of the full bridge depends on the control signals on pins CLK, SU, DD and BD. This is listed in Table 3.

As soon as the supply voltage on pin VDD becomes lower than  $V_{UVLO(VDD)}$  or the supply voltage on pin  $V_{HV}$  becomes lower than  $V_{UVLO(HV)}$ , the IC enters the start-up state again.

#### Full bridge control IC for HID general lighting

| Table 3.   | Driver                                                                              |

|------------|-------------------------------------------------------------------------------------|

| Gate drive | r output voltages as function of the logical levels at the pins BD, SU, DD and CLK. |

| Device state | BD | SU | DD   | CLK                                 | GHL                     | GHR                     | GLL                      | GLR                      |

|--------------|----|----|------|-------------------------------------|-------------------------|-------------------------|--------------------------|--------------------------|

| Start-up     | 1  | -  | -    | -                                   | $0 (= V_{SHL})$         | $0 (= V_{SHR})$         | $0 (= V_{PGND)}$         | $0 (= V_{PGND})$         |

| state        | 0  | -  | -    | -                                   | $0 (= V_{SHL})$         | $0 (= V_{SHR})$         | 1 (= V <sub>VDD</sub> )  | 1 (= V <sub>VDD</sub> )  |

| Oscillation  | 1  | -  | -    | -                                   | 0 (= V <sub>SHL</sub> ) | 0 (= V <sub>SHR</sub> ) | 0 (= V <sub>PGND</sub> ) | 0 (= V <sub>PGND</sub> ) |

| state        | 0  | 0  | -    | -                                   | 0 (= V <sub>SHL</sub> ) | 0 (= V <sub>SHR</sub> ) | 1 (= V <sub>VDD</sub> )  | 1 (= V <sub>VDD</sub> )  |

|              | 0  | 1  | 1    | 1                                   | 0 (= V <sub>SHL</sub> ) | 1 (= V <sub>FSR</sub> ) | 1 (= V <sub>VDD</sub> )  | 0 (= V <sub>PGND</sub> ) |

|              | 0  | 1  | 1    | 0                                   | 1 (= V <sub>FSL</sub> ) | 0 (= V <sub>SHR</sub> ) | 0 (= V <sub>PGND</sub> ) | 1 (= V <sub>VDD</sub> )  |

|              | 0  | 1  | 0[1] | $1 \rightarrow 0^{\underline{[2]}}$ | GHL                     | GHR                     | GLL                      | GLR                      |

<sup>[1]</sup> If pin DD = 0 the bridge enters the state (oscillation state and pin BD = 0 and pin SU = 1) in the predefined position:  $V_{GHL} = V_{FSL}$ ,  $V_{GLR} = V_{VDD}$ ,  $V_{GLL} = V_{PGND}$ , and  $V_{GHR} = V_{SHR}$ .

If there is no external clock available, the internal oscillator can be used. The design equation for the bridge oscillator frequency is shown in Equation 1.

$$f_{bridge} = \frac{1}{K_{osc} \times R_{osc} \times C_{osc}} \tag{1}$$

$R_{osc}$  and  $C_{osc}$  are external components connected to the RC pin ( $R_{osc}$  connected to pin VDD and  $C_{osc}$  connected to pin SGND). In this situation the pins  $V_{DD(CLK)}$ , CLK and  $V_{SS(CLK)}$  can be connected to SGND.

The clock signal, coming from either pin RC or pin CLK, can be divided by two in order to obtain a 50 % duty-cycle gate drive signal. This can be achieved by applying a voltage to the DD input lower than  $V_{\text{IL(DD)}}$  (e.g. connect pin DD to pin SGND).

## 7.4 Non-overlap time

In the full bridge configuration the non-overlap time is defined as the time between turning off the two conducting MOSFETs and turning on the two other MOSFETs. The non-overlap time is realized by means of an adaptive non overlap circuit. With an adaptive non-overlap, the application determines the duration of the non overlap and makes the non-overlap time optimal for each frequency. The non-overlap time is determined by the duration of the falling slope of the relevant half bridge voltage. The occurrence of a slope is sensed internally. The minimum non-overlap time is internally fixed.

### 7.5 Start-up delay

A simple RC filter (R between pin VDD and pin SU; C between pin SU and pin SGND) or a control signal from a processor can be used to make a start-up delay. This can be beneficial for those applications in which building up the high voltage takes a larger amount of time: A start-up delay will ensure that the HID system will not start up before this high voltage has been reached.

<sup>[2]</sup> Only if the level of pin CLK changes from logical 1 to 0, the level of outputs GHL, GHR, GLL and GLR changes.

# Full bridge control IC for HID general lighting

# 7.6 Bridge disable

The bridge disable function can be used to switch off all the MOSFETs as soon as the voltage on pin BD exceeds the bridge disable voltage  $V_{BD}$ . The bridge disable function overrules all the other states.

# 8. Limiting values

Table 4. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134). All voltages are measured with respect to signal ground (pin 14); positive currents flow into the chip. The voltage ratings are valid provided other ratings are not violated.

| Symbol               | Parameter                 | Conditions                                              | Min                        | Max           | Unit              |

|----------------------|---------------------------|---------------------------------------------------------|----------------------------|---------------|-------------------|

| General              |                           |                                                         |                            |               |                   |

| T <sub>amb</sub>     | ambient temperature       |                                                         | -40                        | +125          | °C                |

| T <sub>j</sub>       | junction temperature      |                                                         | -40                        | +150          | °C                |

| T <sub>stg</sub>     | storage temperature       |                                                         | -55                        | +150          | °C                |

| Voltages             |                           |                                                         |                            |               |                   |

| $V_{VDD}$            | voltage on pin VDD        | DC                                                      | 0                          | 14            | V                 |

|                      |                           | maximum pulse time = 100 ns                             | 0                          | 17            | V                 |

| $V_{HV}$             | voltage on pin HV         |                                                         | 0                          | 550           | V                 |

| $V_{SHL}$            | voltage on pin SHL        | with respect to PGND and SGND                           | -3                         | 550           | V                 |

|                      |                           | with respect to SGND;<br>maximum pulse time = 1 $\mu$ s | -14                        | 550           | V                 |

| $V_{SHR}$            | voltage on pin SHR        | with respect to PGND and SGND                           | -3                         | 550           | V                 |

| SHIK                 |                           | with respect to SGND;<br>maximum_pulse_time = 1 μs      | -14                        | 550           | V                 |

| V <sub>FSL</sub>     | voltage on pin FSL        | with respect SHL                                        | 0                          | 14            | V                 |

| V <sub>FSR</sub>     | voltage on pin FSR        | with respect SHR                                        | 0                          | 14            | V                 |

| $V_{GHL}$            | voltage on pin GHL        |                                                         | $V_{SHL}$                  | $V_{FSL}$     | V                 |

| $V_{GHR}$            | voltage on pin GHR        |                                                         | $V_{SHR}$                  | $V_{FSR}$     | V                 |

| $V_{GLL}$            | voltage on pin GLL        |                                                         | $V_{PGND}$                 | $V_{VDD}$     | V                 |

| $V_{GLR}$            | voltage on pin GLR        |                                                         | $V_{PGND}$                 | $V_{VDD}$     | V                 |

| $V_{PGND}$           | voltage on pin PGND       |                                                         | 0                          | 5             | V                 |

| V <sub>SS(CLK)</sub> | CLK ground supply voltage | t < 1 s                                                 | 0                          | 464           | V                 |

| V <sub>DD(CLK)</sub> | CLK supply voltage        | t < 1 s                                                 | 0                          | 464           | V                 |

|                      |                           | with respect to V <sub>SS(CLK)</sub> :                  |                            |               |                   |

|                      |                           | DC                                                      | 0                          | 14            | V                 |

|                      |                           | maximum pulse time = 100 ns                             | 0                          | 17            | V                 |

| V <sub>I</sub>       | input voltage             | pins CLK, SU, BD, and DD; with respe                    | ect to V <sub>SS(CLK</sub> | ):            |                   |

|                      |                           | DC                                                      | 0                          | $V_{VDD}$     | V                 |

|                      |                           | maximum pulse time t = 100 ns                           | 0                          | 17            | V                 |

|                      |                           | pin RC:                                                 |                            |               |                   |

|                      |                           | maximum pulse time = 100 ns                             | 0                          | 17            | V                 |

| SR                   | slew rate                 | pins SHL and SHR                                        | -                          | 6             | V/ns              |

|                      |                           | pin V <sub>SS(CLK)</sub>                                | -                          | 0.5           | V/μs              |

| IBA2037_1            |                           |                                                         |                            | © NXP B.V. 20 | 08. All riahts re |

## Full bridge control IC for HID general lighting

### Table 4. Limiting values ...continued

In accordance with the Absolute Maximum Rating System (IEC 60134). All voltages are measured with respect to signal ground (pin 14); positive currents flow into the chip. The voltage ratings are valid provided other ratings are not violated.

| Symbol           | Parameter                       | Conditions                                                            | Min | Max | Unit |  |  |  |  |

|------------------|---------------------------------|-----------------------------------------------------------------------|-----|-----|------|--|--|--|--|

| Currents         |                                 |                                                                       |     |     |      |  |  |  |  |

| R <sub>osc</sub> | oscillator resistance           | connected between pins VDD and RC                                     | 100 | -   | kΩ   |  |  |  |  |

| ESD              |                                 |                                                                       |     |     |      |  |  |  |  |

| V <sub>ESD</sub> | electrostatic discharge voltage | e human body model:                                                   |     |     |      |  |  |  |  |

| 202              |                                 | HV, $V_{SS(CLK)}$ , $V_{DD(CLK)}$ , CLK, FSL, FSR, GHL, GHR, SHL, SHR | -   | 900 | V    |  |  |  |  |

|                  |                                 | other pins                                                            | -   | 2   | kV   |  |  |  |  |

|                  |                                 | machine model: all pins                                               | -   | 200 | V    |  |  |  |  |

|                  |                                 | charged device model: all pins                                        | -   | 500 | V    |  |  |  |  |

|                  |                                 |                                                                       |     |     |      |  |  |  |  |

## 9. Thermal characteristics

#### Table 5. Thermal characteristics

| Symbol        | Parameter                                   | Conditions  | Тур | Unit |

|---------------|---------------------------------------------|-------------|-----|------|

| $R_{th(j-a)}$ | thermal resistance from junction to ambient | in free air | 100 | K/W  |

# 10. Characteristics

### Table 6. Characteristics

$T_j = 25$  °C; all voltages are measured with respect to signal ground (pin 14); currents are positive when flowing into the IC, Unless otherwise specified.

| Symbol                    | Parameter                              | Conditions                                                                      | Min  | Тур   | Max                                                                                   | Unit           |

|---------------------------|----------------------------------------|---------------------------------------------------------------------------------|------|-------|---------------------------------------------------------------------------------------|----------------|

| High voltage              |                                        |                                                                                 |      |       |                                                                                       |                |

| I <sub>leak</sub>         | leakage current                        | pin HV; $I_{HV}$ (V <sub>HV</sub> = 565 V) – $I_{HV}$ (V <sub>HV</sub> = 500 V) | -    | 0     | 10                                                                                    | μΑ             |

|                           |                                        | pin FSL; $V_{FSL} = V_{SHL} = V_{GHL} = 564 \text{ V}$                          | -    | 0     | 10<br>5<br>0 5<br>0 10<br>10<br>590 825<br>13.2 14.7<br>10.7 12.2<br>2.5 3<br>12 13.5 | μΑ             |

|                           |                                        | pin FSR; $V_{FSR} = V_{SHR} = V_{GHR} = 564 \text{ V}$                          | -    | 0     | 5                                                                                     | μΑ             |

|                           |                                        | pin $V_{SS(CLK)}$ ; $V_{SS(CLK)} = V_{CLK} = 450 \text{ V}$                     | -    | 0     | 10                                                                                    | μΑ             |

|                           |                                        | pin $V_{DD(CLK)}$ ; $V_{DD(CLK)} = V_{CLK} = 464 \text{ V}$                     | -    | 0     | 10                                                                                    | μΑ             |

| Start-up via H            | V pin                                  |                                                                                 |      |       |                                                                                       |                |

| I <sub>I(HV)</sub>        | input current on pin HV                | V <sub>HV</sub> = 80 V                                                          | -    | 590   | 825                                                                                   | μΑ             |

| $V_{\text{startup(HV)}}$  | start-up voltage on pin HV             |                                                                                 | 11.3 | 13.2  | 14.7                                                                                  | V              |

| $V_{\text{UVLO(HV)}}$     | undervoltage lockout voltage on pin HV |                                                                                 | 8.6  | 10.7  | 12.2                                                                                  | V              |

| $V_{hys}$                 | hysteresis voltage                     |                                                                                 | 2    | 2.5   | 3                                                                                     | V              |

| $V_{VDD}$                 | voltage on pin VDD                     | V <sub>HV</sub> = 20 V                                                          | 10.5 | 12    | 13.5                                                                                  | V              |

| Start-up via V            | DD pin                                 |                                                                                 |      |       |                                                                                       |                |

| I <sub>I(VDD)</sub>       | input current on pin VDD               | V <sub>VDD</sub> = 8.25 V                                                       | -    | 500   | 800                                                                                   | μΑ             |

| $V_{\text{startup(VDD)}}$ | start-up voltage on pin<br>VDD         |                                                                                 | 8.25 | 9.0   | 9.75                                                                                  | V              |

| UBA2037_1                 |                                        |                                                                                 |      | © NXF | P B.V. 2008. All                                                                      | rights reserve |

# Full bridge control IC for HID general lighting

Table 6.

Characteristics ...continued

$T_j = 25$  °C; all voltages are measured with respect to signal ground (pin 14); currents are positive when flowing into the IC, Unless otherwise specified.

| Symbol                             | Parameter                                      | Conditions                                                                                                                                                            | Min  | Тур | Max  | Unit |

|------------------------------------|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|------|

| $V_{\text{UVLO(VDD)}}$             | undervoltage lockout<br>voltage on pin VDD     |                                                                                                                                                                       | 5.75 | 6.5 | 7.25 | V    |

| V <sub>hys</sub>                   | hysteresis voltage                             | V <sub>FSL</sub> = V <sub>FSR</sub> = 12 V                                                                                                                            | 2    | 2.5 | 3    | V    |

| gate drivers                       |                                                |                                                                                                                                                                       |      |     |      |      |

| R <sub>on</sub>                    | on-state resistance                            | GHR and GHL drivers;<br>$V_{FSL} = V_{FSR} = 12 \text{ V};$<br>$V_{SHL} = V_{SHR} = 0 \text{ V};$<br>$I_{GHL} = I_{GHR} = -50 \text{ mA}$                             | -    | 20  | 42   | Ω    |

|                                    |                                                | GLR and GHL drivers; $V_{VDD}$ = 12 V; $V_{PGND}$ = 0 V; $I_{GLL}$ = $I_{GLR}$ = -50 mA                                                                               | -    | 20  | 42   | Ω    |

| R <sub>off</sub>                   | off-state resistance                           | GHR and GHL drivers;<br>$V_{FSL} = V_{FSR} = 12 \text{ V};$<br>$V_{SHL} = V_{SHR} = 0 \text{ V};$<br>$I_{GHL} = I_{GHR} = 50 \text{ mA}$                              | -    | 12  | 26   | Ω    |

|                                    |                                                | GLR and GLL drivers; $V_{VDD} = 12 \text{ V}$ ; $V_{PGND} = 0 \text{ V}$ ; $I_{GLL} = I_{GLR} = 50 \text{ mA}$                                                        | -    | 12  | 26   | Ω    |

| I <sub>O(source)</sub>             | output source current                          | $\begin{split} V_{FSL} &= V_{FSR} = V_{VDD} = 12 \text{ V}; \\ V_{SHL} &= V_{SHR} = 0 \text{ V}; \\ V_{GHL} &= V_{GHR} = V_{GLL} = V_{GLR} = 8 \text{ V} \end{split}$ | -    | 200 | -    | mA   |

| I <sub>O(sink)</sub>               | output sink current                            | $V_{FSL} = V_{FSR} = V_{VDD} = 12 \text{ V};$<br>$V_{SHL} = V_{SHR} = 0 \text{ V};$<br>$V_{GHL} = V_{GHR} = V_{GLL} = V_{GLR} = 8 \text{ V}$                          | -    | 200 | -    | mA   |

| V <sub>d(bs)</sub>                 | bootstrap diode voltage                        | current on diode = 1 mA                                                                                                                                               | 0.8  | 1.0 | 1.2  | V    |

| dV/dt                              | rate of change of voltage                      | absolute values                                                                                                                                                       | 5    | 15  | 25   | V/μs |

| t <sub>no</sub>                    | non-overlap time                               |                                                                                                                                                                       | 600  | 900 | 1300 | ns   |

| $V_{UVLO}$                         | undervoltage lockout<br>voltage                | high side driver                                                                                                                                                      | -    | 4.0 | 5.5  | V    |

| I <sub>FS</sub>                    | current on pin FS                              | $V_{FSL} = V_{FSR} = 12 \text{ V};$<br>$V_{SHL} = V_{SHR} = 0 \text{ V}$                                                                                              | 1    | 4   | 7    | μΑ   |

| I <sub>FSL</sub> /I <sub>FSR</sub> | current on pin FSL to current on pin FSR ratio |                                                                                                                                                                       | 0.8  | -   | 1.2  |      |

| DD input                           |                                                |                                                                                                                                                                       |      |     |      |      |

| $V_{IH(DD)}$                       | HIGH-level input voltage on pin DD             | $V_{VDD} = 12 \text{ V}$                                                                                                                                              | 6    | 4.5 | -    | V    |

| $V_{\text{IL}(\text{DD})}$         | LOW-level input voltage on pin DD              | $V_{VDD} = 12 \text{ V}$                                                                                                                                              | -    | -   | 3    | V    |

| I <sub>I</sub>                     | input current                                  | V <sub>VDD</sub> = 12 V                                                                                                                                               | -    | 0   | 1    | μΑ   |

| SU input                           |                                                |                                                                                                                                                                       |      |     |      |      |

| V <sub>startup</sub>               | start-up voltage                               | V <sub>VDD</sub> = 12 V                                                                                                                                               | 1    | 1.3 | 1.5  | V    |

| V <sub>hys</sub>                   | hysteresis voltage                             | V <sub>VDD</sub> = 12 V                                                                                                                                               | -    | 100 | -    | μV   |

| l <sub>l</sub>                     | input current                                  | V <sub>VDD</sub> = 12 V                                                                                                                                               | -    | 0   | 1    | μΑ   |

| CLK input                          |                                                |                                                                                                                                                                       |      |     |      |      |

| V <sub>IH(CLK)</sub>               | HIGH-level input voltage on pin CLK            | $V_{SS(CLK)} = 0 \text{ V}; V_{DD(CLK)} = 12 \text{ V}$                                                                                                               | 0.9  | 1.6 | 2.7  | V    |

## Full bridge control IC for HID general lighting

Table 6.

Characteristics ...continued

$T_j = 25$  °C; all voltages are measured with respect to signal ground (pin 14); currents are positive when flowing into the IC, Unless otherwise specified.

| Symbol                | Parameter                        | Conditions                                              | Min  | Тур  | Max  | Unit |

|-----------------------|----------------------------------|---------------------------------------------------------|------|------|------|------|

| $V_{hys}$             | hysteresis voltage               | $V_{SS(CLK)} = 0 \text{ V}; V_{DD(CLK)} = 12 \text{ V}$ | -    | 100  | -    | mV   |

| II                    | input current                    |                                                         | -    | 0    | 1    | μΑ   |

| f <sub>bridge</sub>   | bridge frequency                 | V <sub>RC</sub> = 0 V                                   | -    | -    | 200  | kHz  |

| supply for CLK        |                                  |                                                         |      |      |      |      |

| I <sub>DD(CLK)</sub>  | CLK supply current               | $V_{SS(CLK)} = 0 \text{ V}; V_{DD(CLK)} = 14 \text{ V}$ | -    | 420  | 625  | μΑ   |

| V <sub>DD(CLK)</sub>  | CLK supply voltage               | $V_{SS(CLK)} = 0 V$                                     | 5.75 | -    | 14   | V    |

| BD input              |                                  |                                                         |      |      |      |      |

| $V_{BD}$              | voltage on pin BD                |                                                         | 1.23 | 1.29 | 1.35 | V    |

| II                    | input current                    |                                                         | -    | 0    | 1    | μΑ   |

| Internal oscillato    | or                               |                                                         |      |      |      |      |

| f <sub>osc(int)</sub> | internal oscillator<br>frequency | $V_{CLK} = 0 \text{ V}; V_{SS(CLK)} = 0 \text{ V}$      | -    | -    | 100  | kHz  |

| K <sub>osc</sub>      | oscillator constant              | f <sub>bridge</sub> = 500 Hz                            | 0.89 | 0.97 | 1.05 |      |

- (1) Temperature =  $-25 \, ^{\circ}\text{C}$

- (2) Temperature = 25 °C

- (3) Temperature = 125  $^{\circ}$ C

Fig 4. Typical  $I_I$  (pin HV) when VDD connected to SGND, as function of  $V_{HV}$  and temperature

**UBA2037 NXP Semiconductors**

## Full bridge control IC for HID general lighting

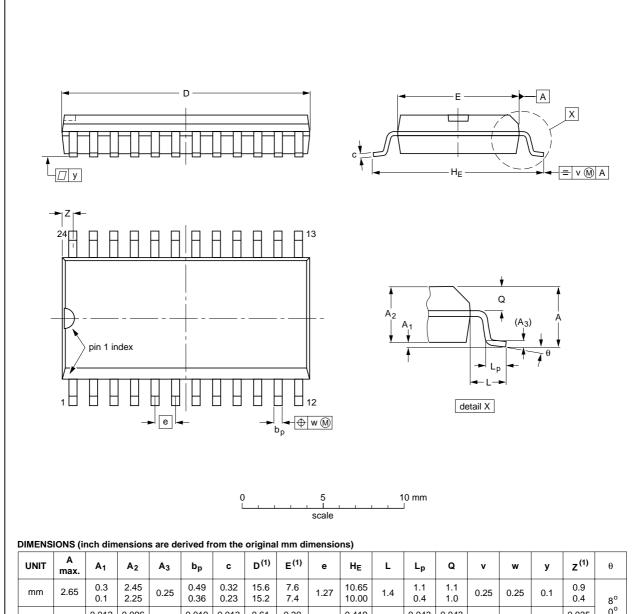

# 11. Package outline

## SO24: plastic small outline package; 24 leads; body width 7.5 mm

SOT137-1

| UNIT   | A<br>max. | A <sub>1</sub> | A <sub>2</sub> | A <sub>3</sub> | bp             | С            | D <sup>(1)</sup> | E <sup>(1)</sup> | е    | HE             | L     | Lp             | Q              | v    | w    | у     | z <sup>(1)</sup> | θ  |

|--------|-----------|----------------|----------------|----------------|----------------|--------------|------------------|------------------|------|----------------|-------|----------------|----------------|------|------|-------|------------------|----|

| mm     | 2.65      | 0.3<br>0.1     | 2.45<br>2.25   | 0.25           | 0.49<br>0.36   | 0.32<br>0.23 | 15.6<br>15.2     | 7.6<br>7.4       | 1.27 | 10.65<br>10.00 | 1.4   | 1.1<br>0.4     | 1.1<br>1.0     | 0.25 | 0.25 | 0.1   | 0.9<br>0.4       | 8° |

| inches | 0.1       | 0.012<br>0.004 | 0.096<br>0.089 | 0.01           | 0.019<br>0.014 |              | 0.61<br>0.60     | 0.30<br>0.29     | 0.05 | 0.419<br>0.394 | 0.055 | 0.043<br>0.016 | 0.043<br>0.039 | 0.01 | 0.01 | 0.004 | 0.035<br>0.016   | 0° |

#### Note

1. Plastic or metal protrusions of 0.15 mm (0.006 inch) maximum per side are not included.

|        | REFER  | EUROPEAN | ISSUE DATE |            |                                 |  |

|--------|--------|----------|------------|------------|---------------------------------|--|

| IEC    | JEDEC  | JEITA    |            | PROJECTION | ISSUE DATE                      |  |

| 075E05 | MS-013 |          |            |            | <del>99-12-27</del><br>03-02-19 |  |

| -      |        |          |            |            | IEC JEDEC JEITA PROJECTION      |  |

Package outline SO24 (SOT137-1) Fig 5.

UBA2037 1 © NXP B.V. 2008. All rights reserved.

**UBA2037 NXP Semiconductors**

## Full bridge control IC for HID general lighting

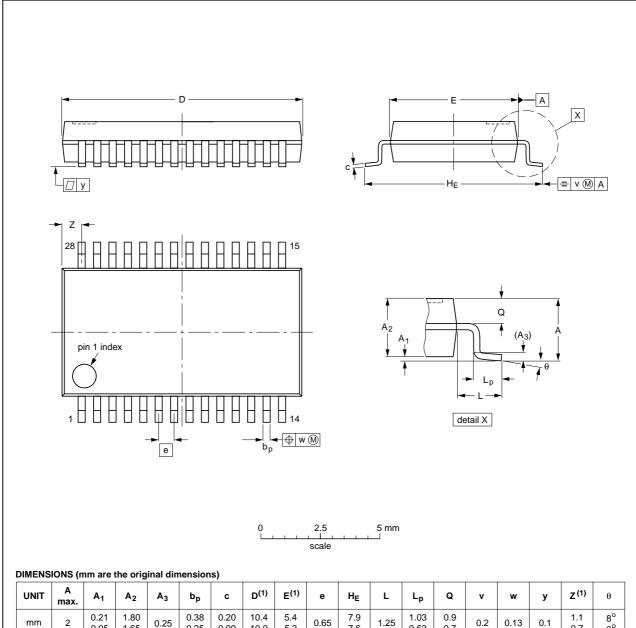

SSOP28: plastic shrink small outline package; 28 leads; body width 5.3 mm

SOT341-1

| UNIT | A<br>max. | A <sub>1</sub> | A <sub>2</sub> | A <sub>3</sub> | bp           | U            | D <sup>(1)</sup> | E <sup>(1)</sup> | e    | HE         | ٦    | Lp           | ď          | >   | w    | у   | Z <sup>(1)</sup> | θ        |

|------|-----------|----------------|----------------|----------------|--------------|--------------|------------------|------------------|------|------------|------|--------------|------------|-----|------|-----|------------------|----------|

| mm   | 2         | 0.21<br>0.05   | 1.80<br>1.65   | 0.25           | 0.38<br>0.25 | 0.20<br>0.09 | 10.4<br>10.0     | 5.4<br>5.2       | 0.65 | 7.9<br>7.6 | 1.25 | 1.03<br>0.63 | 0.9<br>0.7 | 0.2 | 0.13 | 0.1 | 1.1<br>0.7       | 8°<br>0° |

#### Note

1. Plastic or metal protrusions of 0.2 mm maximum per side are not included.

|     |        | REFERENCES |  |            |                                 |  |  |  |

|-----|--------|------------|--|------------|---------------------------------|--|--|--|

| IEC | JEDEC  | JEITA      |  | PROJECTION | ISSUE DATE                      |  |  |  |

|     | MO-150 |            |  |            | <del>99-12-27</del><br>03-02-19 |  |  |  |

|     | IEC    |            |  |            |                                 |  |  |  |

Package outline SSOP28 (SOT341-1) Fig 6.

UBA2037\_1 © NXP B.V. 2008. All rights reserved.

# Full bridge control IC for HID general lighting

# 12. Revision history

## Table 7. Revision history

| Document ID | Release date | Data sheet status  | Change notice | Supersedes |

|-------------|--------------|--------------------|---------------|------------|

| UBA2037_1   | 20081030     | Product data sheet | -             | -          |

## Full bridge control IC for HID general lighting

# 13. Legal information

#### 13.1 Data sheet status

| Document status[1][2]          | Product status[3] | Definition                                                                            |

|--------------------------------|-------------------|---------------------------------------------------------------------------------------|

| Objective [short] data sheet   | Development       | This document contains data from the objective specification for product development. |

| Preliminary [short] data sheet | Qualification     | This document contains data from the preliminary specification.                       |

| Product [short] data sheet     | Production        | This document contains the product specification.                                     |

- [1] Please consult the most recently issued document before initiating or completing a design.

- [2] The term 'short data sheet' is explained in section "Definitions"

- [3] The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL <a href="http://www.nxp.com">http://www.nxp.com</a>.

#### 13.2 Definitions

Draft — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.

### 13.3 Disclaimers

**General** — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in medical, military, aircraft, space or life support equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental

damage. NXP Semiconductors accepts no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

**Quick reference data** — The Quick reference data is an extract of the product data given in the Limiting values and Characteristics sections of this document, and as such is not complete, exhaustive or legally binding.

Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) may cause permanent damage to the device. Limiting values are stress ratings only and operation of the device at these or any other conditions above those given in the Characteristics sections of this document is not implied. Exposure to limiting values for extended periods may affect device reliability.

Terms and conditions of sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at <a href="http://www.nxp.com/profile/terms">http://www.nxp.com/profile/terms</a>, including those pertaining to warranty, intellectual property rights infringement and limitation of liability, unless explicitly otherwise agreed to in writing by NXP Semiconductors. In case of any inconsistency or conflict between information in this document and such terms and conditions, the latter will prevail.

**No offer to sell or license** — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

#### 13.4 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

### 14. Contact information

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

UBA2037\_1 © NXP B.V. 2008. All rights reserved.

**UBA2037 NXP Semiconductors**

# Full bridge control IC for HID general lighting

# 15. Contents

| 1    | General description       |

|------|---------------------------|

| 2    | Features                  |

| 3    | Applications              |

| 4    | Ordering information 2    |

| 5    | Block diagram 2           |

| 6    | Pinning information       |

| 6.1  | Pinning                   |

| 6.2  | Pin description           |

| 7    | Functional description 4  |

| 7.1  | Supply voltage 4          |

| 7.2  | Start-up 4                |

| 7.3  | Oscillation state 4       |

| 7.4  | Non-overlap time 5        |

| 7.5  | Start-up delay 5          |

| 7.6  | Bridge disable 6          |

| 8    | Limiting values 6         |

| 9    | Thermal characteristics 7 |

| 10   | Characteristics 7         |

| 11   | Package outline           |

| 12   | Revision history          |

| 13   | Legal information         |

| 13.1 | Data sheet status         |

| 13.2 | Definitions               |

| 13.3 | Disclaimers               |

| 13.4 | Trademarks                |

| 14   | Contact information       |

| 15   | Contents                  |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

© NXP B.V. 2008.

All rights reserved.

For more information, please visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: 30 October 2008 Document identifier: UBA2037\_1