## **General Description**

The AOZ8318 is a transient voltage suppressor array designed to protect high speed data lines from ESD and lightning.

This AOZ8318 incorporates eight surge rated, low capacitance steering diodes and a TVS in a single package. During transient conditions, the steering diodes direct the transient to either the positive side of the power supply line or to ground. The AOZ8318 may be used to meet the ESD immunity requirements of IEC 61000-4-2, Level 4 and IEC 61000-4-5. The TVS diodes provide effective suppression of ESD voltages: ±30 kV (air discharge) and ±30 kV (contact discharge).

The AOZ8318 comes in a Halogen Free and RoHS compliant DFN-10 2.6 mm x 2.6 mm package and is rated over a -40 °C to +85 °C ambient temperature range. The AOZ8318 is compatible with both lead free and SnPb assembly techniques. The small size, low capacitance and high ESD protection makes the AOZ8318 ideal for protecting high speed video and data communication interfaces.

#### **Features**

- ESD protection for high-speed data lines:

- IEC 61000-4-2, level 4 (ESD) immunity test

- ±30 kV (air discharge) and ±30 kV (contact discharge)

- IEC 61000-4-4 (EFT) 40 A (5/50 ns)

- IEC 61000-4-5 (Lightning) 25 A

- Human Body Model (HBM) ±30 kV

- Small package saves board space

- Low insertion loss

- Protects four I/O lines

- Low clamping voltage

- Low operating voltage: 2.5 V

- Green product

- Pb-free device

## **Applications**

- 10/100/1000 Ethernet

- USB 2.0 power and data line protection

- Video graphics cards

- Monitors and flat panel displays

- Digital Video Interface (DVI)

- T1/E1 telecom ports

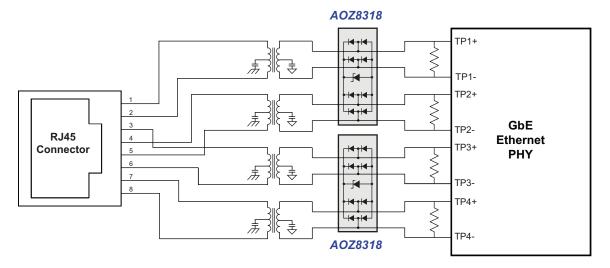

# **Typical Application**

Figure 1. 10/100/1000 Ethernet Port Connection

# **Ordering Information**

| Part Number | Ambient Temperature Range | Package                | Environmental |  |  |

|-------------|---------------------------|------------------------|---------------|--|--|

| AOZ8318DI   | -40 °C to +85 °C          | 2.6 mm x 2.6 mm DFN-10 | Green Product |  |  |

AOS Green Products (with "L" suffix) use reduced levels of Halogens, and are also RoHS compliant. Please visit www.aosmd.com/media/AOSGreenPolicy.pdf for additional information.

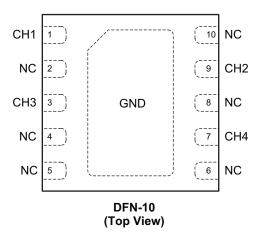

# **Pin Configuration**

| Pin Number        | Description        |

|-------------------|--------------------|

| 1, 3, 7, 9        | Input/Output lines |

| 2, 4, 5, 6, 8, 10 | No connection      |

| Center Tab        | Ground             |

# **Absolute Maximum Ratings**

Exceeding the Absolute Maximum ratings may damage the device.

| Parameter                                                       | Rating            |

|-----------------------------------------------------------------|-------------------|

| VP – GND                                                        | 2.5 V             |

| Peak Pulse Current (I <sub>PP</sub> ), t <sub>P</sub> = 8/20 μs | 25 A              |

| Peak Power Dissipation (8 x 20 μs@ 25 °C)                       | 350 W             |

| Storage Temperature (T <sub>S</sub> )                           | -65 °C to +150 °C |

| ESD Rating per IEC61000-4-2, Contact <sup>(1)</sup>             | ±30 kV            |

| ESD Rating per IEC61000-4-2, Air <sup>(1)</sup>                 | ±30 kV            |

| ESD Rating per Human Body Model <sup>(2)</sup>                  | ±30 kV            |

#### Notes:

- 1. IEC 61000-4-2 discharge with C\_Discharge = 150 pF, R\_Discharge = 330  $\Omega.$

- 2. Human Body Discharge per MIL-STD-883, Method 3015  $C_{Discharge}$  = 100 pF,  $R_{Discharge}$  = 1.5 k $\Omega$ .

# **Maximum Operating Ratings**

|                      | Parameter     | Rating            |

|----------------------|---------------|-------------------|

| Junction Temperature | $(T_{\sf J})$ | -40 °C to +125 °C |

Rev. 2.0 October 2014 **www.aosmd.com** Page 2 of 8

## **Electrical Characteristics**

$T_A = 25$ °C unless otherwise specified.

| Symbol           | Parameter                                 | Conditions                                                            | Min. | Тур. | Max. | Units |

|------------------|-------------------------------------------|-----------------------------------------------------------------------|------|------|------|-------|

| V <sub>RWM</sub> | Reverse Working Voltage                   | Between any I/O pin and GND <sup>(4)</sup>                            |      |      | 2.5  | V     |

| I <sub>R</sub>   | Reverse Leakage Current                   | V <sub>RWM</sub> = 2.5 V, between any I/O pin and GND                 |      |      | 1    | μΑ    |

| $V_{BR}$         | Reverse Breakdown Voltage                 | I <sub>T</sub> = 100 μA                                               | 2.8  |      |      | V     |

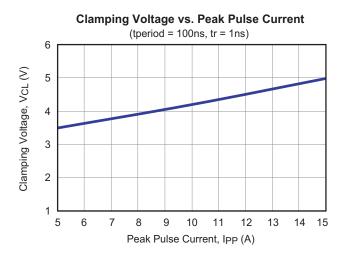

| V <sub>CL</sub>  | Channel Clamp Voltage Positive Transients | $I_{PP}$ = 5 A, tp = 100 ns, any I/O pin to Ground <sup>(3)(6)</sup>  |      |      | 3.5  | V     |

|                  | Negative Transient                        |                                                                       |      |      | -3.5 | V     |

|                  | Channel Clamp Voltage                     | $I_{PP} = 10 \text{ A, tp} = 100 \text{ ns, any I/O pin to}$          |      |      |      |       |

|                  | Positive Transients                       | Ground <sup>(3)(6)</sup>                                              |      |      | 4.2  | V     |

|                  | Negative Transient                        |                                                                       |      |      | -5   | V     |

|                  | Channel Clamp Voltage                     | $I_{PP} = 15 \text{ A}$ , tp = 100 ns, any I/O pin to                 |      |      |      |       |

|                  | Positive Transients                       | Ground <sup>(3)(6)</sup>                                              |      |      | 5    | V     |

|                  | Negative Transient                        |                                                                       |      |      | -6.5 | V     |

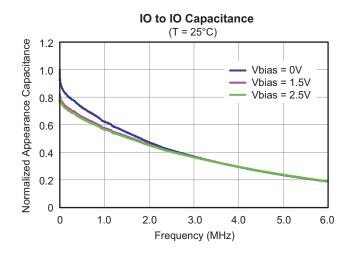

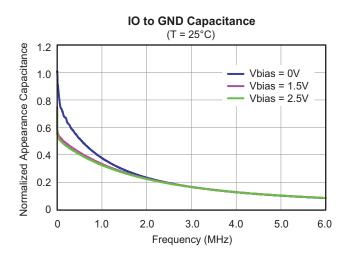

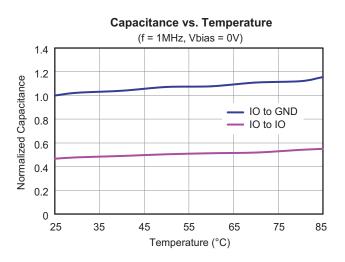

| C <sub>j</sub>   | Junction Capacitance                      | $V_R = 0 \text{ V}, f = 1 \text{ MHz}, \text{ any I/O pin to Ground}$ |      | 3.0  | 4.5  | pF    |

|                  |                                           | $V_R = 0 \text{ V, f} = 1 \text{ MHz, between I/O pins}^{(3)}$        |      | 1.4  |      | pF    |

#### Notes:

- 3. These specifications are guaranteed by design.

- 4. The working peak reverse voltage,  $V_{RWM}$ , should be equal to or greater than the DC or continuous peak operating voltage level.

- 5.  $V_{BR}$  is measured at the pulse test current  $I_{T}$ .

- 6. Measurements performed using a 100 ns Transmission Line Pulse (TLP) system.

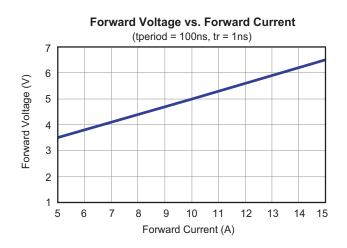

# **Typical Performance Characteristics**

Rev. 2.0 October 2014 **www.aosmd.com** Page 4 of 8

## **Application Information**

The AOZ8318 TVS is design to protect four data lines from fast damaging transient over-voltage by clamping the over-voltage to a reference. When the transient on a protected data line exceeds the reference voltage, the steering diode is forward bias and conducts harmful ESD transients away from the sensitive circuitry under protection.

#### **PCB Layout Guidelines**

Printed circuit board layout is the key to achieving the highest level of surge immunity on power and data lines. The location of the protection devices on the PCB is the simplest and most important design rule to follow. The AOZ8318 devices should be located as close as possible to the noise source. The placement of the AOZ8318 devices should be used on all data and power lines that enter or exit the PCB at the I/O connector. In most systems, surge pulses occur on data and power lines that enter the PCB through the I/O connector. Placing the AOZ8318 devices as close as possible to the noise source ensures that a surge voltage will be clamped before the pulse can be coupled into adjacent PCB traces. In addition, the PCB should use the shortest possible traces. A short trace length equates to low impedance, which ensures that the surge energy will be dissipated by the AOZ8318 device. Long signal traces will act as antennas to receive energy from fields that are produced by the ESD pulse. By keeping line lengths as short as possible, the efficiency of the line to act as an antenna for ESD related fields is reduced.

Minimize interconnecting line lengths by placing devices with the most interconnect as close together as possible. The protection circuits should shunt the surge voltage to either the reference or chassis ground. Shunting the surge voltage directly to the IC's signal ground can cause ground bounce. The clamping performance of TVS diodes on a single ground PCB can be improved by minimizing the impedance with relatively short and wide ground traces. The PCB layout and IC package parasitic inductances can cause significant overshoot to the TVS's clamping voltage. The inductance of the PCB can be reduced by using short trace lengths and multiple layers with separate ground and power planes. One effective method to minimize loop problems is to incorporate a ground plane in the PCB design. The AOZ8318 low capacitance TVS is designed to protect four high speed data transmission lines from transient over-voltages by clamping them to a fixed reference. The low inductance and construction minimizes voltage overshoot during high current surges. When the voltage on the protected line exceeds the reference voltage the internal steering diodes are forward biased, conducting the transient current away from the sensitive circuitry.

Good circuit board layout is critical for the suppression of ESD induced transients. The following guidelines are recommended:

- 1. Place the TVS near the I/O terminals or connectors to restrict transient coupling.

- 2. Fill unused portions of the PCB with ground plane.

- Minimize the path length between the TVS and the protected line.

- 4. Minimize all conductive loops including power and ground loops.

- 5. The ESD transient return path to ground should be kept as short as possible.

- 6. Never run critical signals near board edges.

- 7. Use ground planes whenever possible.

- 8. Avoid running critical signal traces (clocks, resets, etc.) near PCB edges.

- 9. Separate chassis ground traces from components and signal traces by at least 4 mm.

- Keep the chassis ground trace length-to-width ratio

5:1 to minimize inductance.

- 11. Protect all external connections with TVS diodes.

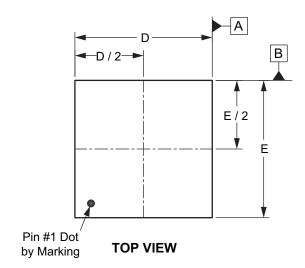

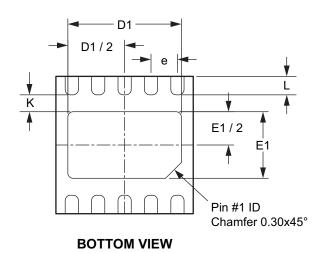

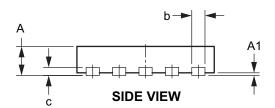

# Package Dimensions, DFN 2.6x 2.6, 10L, EP1\_S

## **RECOMMENDED LAND PATTERN**

## **Dimensions in millimeters**

| Symbols | Min.     | Nom.     | Max. |  |  |  |

|---------|----------|----------|------|--|--|--|

| Α       | 0.50     | 0.55     | 0.60 |  |  |  |

| A1      | 0.00     | _        | 0.05 |  |  |  |

| b       | 0.20     | 0.25     | 0.30 |  |  |  |

| С       | 0        | .152 REI | F.   |  |  |  |

| D       | 2.55     | 2.60     | 2.65 |  |  |  |

| D1      | 2.10     | 2.15     | 2.20 |  |  |  |

| E       | 2.55     | 2.60     | 2.65 |  |  |  |

| E1      | 1.21     | 1.26     | 1.31 |  |  |  |

| е       | 0.50 BSC |          |      |  |  |  |

| K       | 0.32 REF |          |      |  |  |  |

| L       | 0.30     | 0.35     | 0.40 |  |  |  |

## **Dimensions in inches**

| Symbols | Min.      | Nom.     | Max.  |  |  |  |  |  |  |

|---------|-----------|----------|-------|--|--|--|--|--|--|

| Α       | 0.020     | 0.022    | 0.024 |  |  |  |  |  |  |

| A1      | 0.000     | _        | 0.002 |  |  |  |  |  |  |

| b       | 0.008     | 0.010    | 0.012 |  |  |  |  |  |  |

| С       | 0.        | .006 REI | =.    |  |  |  |  |  |  |

| D       | 0.100     | 0.102    | 0.104 |  |  |  |  |  |  |

| D1      | 0.083     | 0.085    | 0.087 |  |  |  |  |  |  |

| E       | 0.100     | 0.102    | 0.104 |  |  |  |  |  |  |

| E1      | 0.048     | 0.050    | 0.052 |  |  |  |  |  |  |

| е       | 0.020 BSC |          |       |  |  |  |  |  |  |

| K       | 0         | .013 BS  | С     |  |  |  |  |  |  |

| L       | 0.012     | 0.014    | 0.016 |  |  |  |  |  |  |

|                               | <b>⋖</b> 2.35 <b>►</b> |

|-------------------------------|------------------------|

| <b>↓</b>                      | 1.175                  |

| 0.45                          | 0.32                   |

| 1.26                          | 2.35                   |

| Pin #1 ID<br>Chamfer 0.20x45° |                        |

| UNIT: mm                      | - 0.25                 |

## Note:

1. Controlling dimension is millimeter. Coverted inch dimensions are not necessarily exact

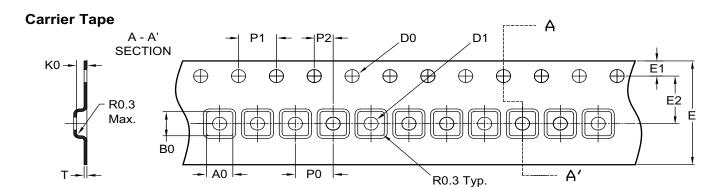

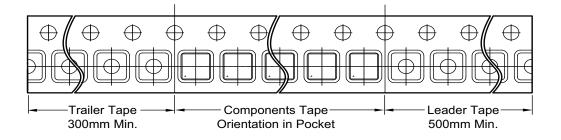

# Tape and Reel Dimensions, DFN 2.6x2.6, 10L

UNIT: mm

Feeding Direction

| Package | Т     | В0    | A0    | K0    | D0        | D1    | E    | E1    | E2    | P0    | P1    | P2    |

|---------|-------|-------|-------|-------|-----------|-------|------|-------|-------|-------|-------|-------|

| DFN     | 0.30  | 2.80  | 2.80  | 1.10  | ø1.50     | ø1.50 | 12.0 | 1.75  | 5.50  | 4.00  | 4.00  | 2.00  |

| 2.6x2.6 | ±0.05 | ±0.10 | ±0.10 | ±0.10 | +0.1/-0.0 | Min.  | ±0.3 | ±0.10 | ±0.05 | ±0.10 | ±0.10 | ±0.05 |

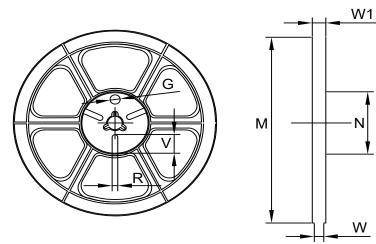

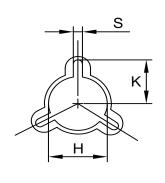

#### Reel

UNIT: mm

| Tape Size | Reel Size | M            | N          | W          | W1   | н             | K             | S           | G | R | V |

|-----------|-----------|--------------|------------|------------|------|---------------|---------------|-------------|---|---|---|

| 12mm      | ø330      | ø179<br>±1.0 | 60<br>±0.5 | 13<br>±0.5 | 17.0 | ø13.0<br>±0.2 | 10.5<br>±0.25 | 2.0<br>±0.2 |   |   |   |

# Leader / Trailer & Orientation

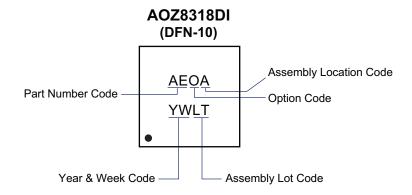

## **Part Marking**

#### **LEGAL DISCLAIMER**

Applications or uses as critical components in life support devices or systems are not authorized. AOS does not assume any liability arising out of such applications or uses of its products. AOS reserves the right to make changes to product specifications without notice. It is the responsibility of the customer to evaluate suitability of the product for their intended application. Customer shall comply with applicable legal requirements, including all applicable export control rules, regulations and limitations.

AOS' products are provided subject to AOS' terms and conditions of sale which are set forth at: http://www.aosmd.com/terms and conditions of sale

#### LIFE SUPPORT POLICY

ALPHA AND OMEGA SEMICONDUCTOR PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS.

As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- 2. A critical component in any component of a life support, device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

Rev. 2.0 October 2014 **www.aosmd.com** Page 8 of 8