|

|

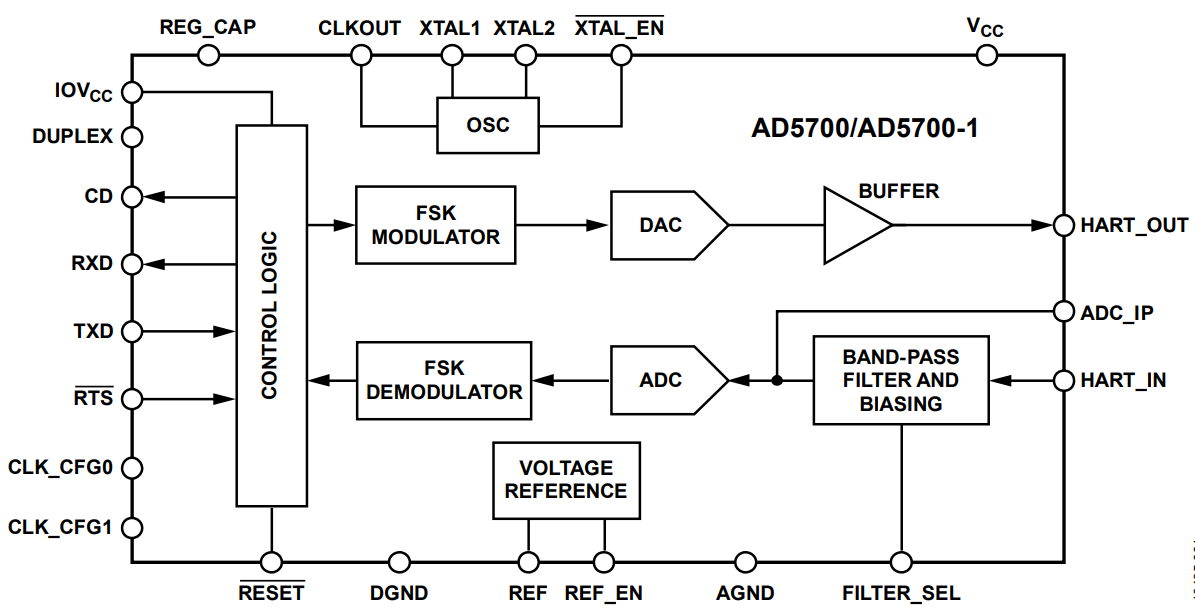

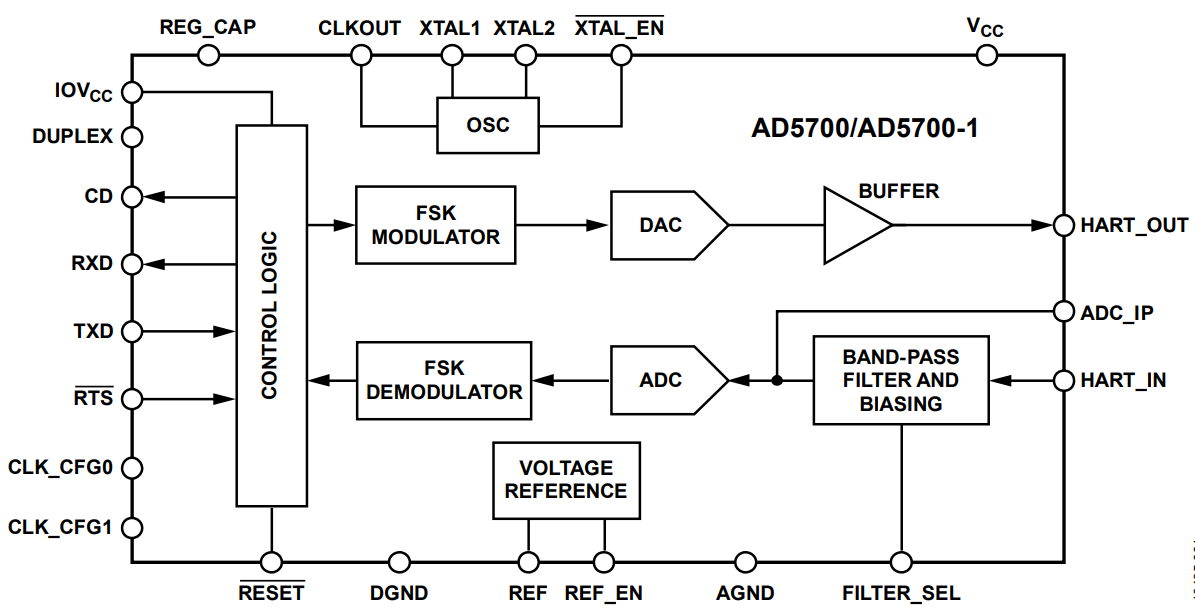

| • HART-compliant fully integrated FSK modem |

| • 1200 Hz and 2200 Hz sinusoidal shift frequencies |

| • 115 µA maximum supply current in receive mode |

| • Suitable for intrinsically safe applications |

• Integrated receive band-pass filter

- Minimal external components required |

• Clocking optimized for various system configurations

- Ultralow power crystal oscillator (60 µA maximum)

- External CMOS clock source

- Precision internal oscillator (AD5700-1only) |

| • Buffered HART output—extra drive capability |

| • 8 kV HBM ESD rating |

| • 1.71 V to 5.5 V power supply |

| • 1.71 V to 5.5 V interface |

| • −40°C to +125°C operation |

| • 4 mm × 4 mm LFCSP package |

| • HART physical layer compliant |

| • UART interface |

|

| CATALOG |

| AD5700-1BCPZ-RL7 COUNTRY OF ORIGIN |

| AD5700-1BCPZ-RL7 PARAMETRIC INFO |

| AD5700-1BCPZ-RL7 PACKAGE INFO |

| AD5700-1BCPZ-RL7 MANUFACTURING INFO |

| AD5700-1BCPZ-RL7 PACKAGING INFO |

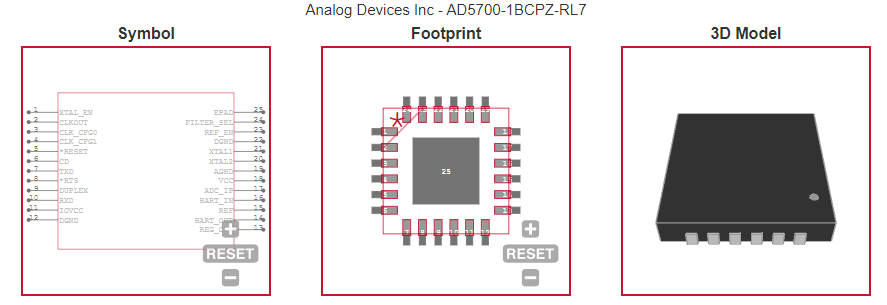

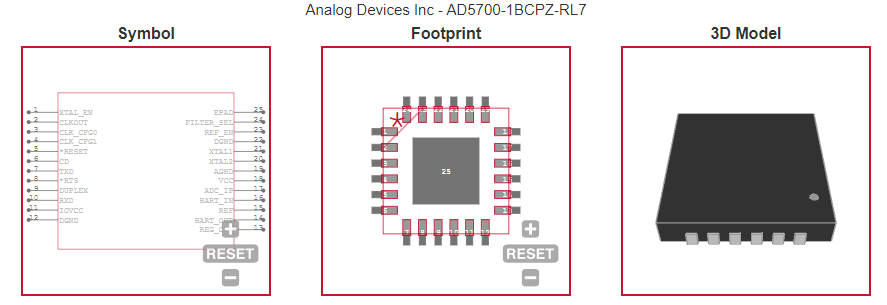

| AD5700-1BCPZ-RL7 ECAD MODELS |

| AD5700-1BCPZ-RL7 FUNCTIONAL BLOCK DIAGRAM |

| AD5700-1BCPZ-RL7 APPLICATIONS |

|

| COUNTRY OF ORIGIN |

| Malaysia |

| Korea (Republic of) |

| China |

|

| PARAMETRIC INFO |

| Main Category |

Single Chip |

| Subcategory |

HART Modem |

| Modulation Technique |

FSK |

| Minimum Operating Temperature (°C) |

-40 |

| Maximum Operating Temperature (°C) |

125 |

| Supplier Temperature Grade |

Industrial |

| Maximum Storage Temperature (°C) |

150 |

| Minimum Storage Temperature (°C) |

-65 |

| Power Supply Type |

Analog |

| Typical Operating Supply Voltage (V) |

3.3|5 |

| Minimum Operating Supply Voltage (V) |

2 |

| Maximum Operating Supply Voltage (V) |

5.5 |

|

|

| PACKAGE INFO |

| Supplier Package |

LFCSP EP |

| Basic Package Type |

Non-Lead-Frame SMT |

| Pin Count |

24 |

| Lead Shape |

No Lead |

| PCB |

24 |

| Tab |

N/R |

| Pin Pitch (mm) |

0.5 |

| Package Length (mm) |

4 |

| Package Width (mm) |

4 |

| Package Height (mm) |

0.73 |

| Package Diameter (mm) |

N/R |

| Package Overall Length (mm) |

4 |

| Package Overall Width (mm) |

4 |

| Package Overall Height (mm) |

0.75 |

| Seated Plane Height (mm) |

0.75 |

| Mounting |

Surface Mount |

| Package Weight (g) |

N/A |

| Package Material |

Plastic |

| Package Description |

Lead Frame Chip Scale Package, Exposed Pad |

| Package Family Name |

CSP |

| Jedec |

MO-220WGGD-8 |

| Package Outline |

Link to Datasheet |

|

|

| MANUFACTURING INFO |

| MSL |

3 |

| Maximum Reflow Temperature (°C) |

260 |

| Reflow Solder Time (Sec) |

30 |

| Number of Reflow Cycle |

3 |

| Standard |

J-STD-020D |

| Maximum Wave Temperature (°C) |

N/R |

| Wave Solder Time (Sec) |

N/R |

| Lead Finish(Plating) |

Matte Sn annealed |

| Under Plating Material |

Ag |

| Terminal Base Material |

N/A |

|

|

| PACKAGING INFO |

| Packaging Suffix |

RL7 |

| Packaging |

Tape and Reel |

| Quantity Of Packaging |

1500 |

| Reel Diameter (in) |

7 |

| Packaging Document |

Link to Datasheet |

|

|

| ECAD MODELS |

|

|

| FUNCTIONAL BLOCK DIAGRAM |

|

|

| APPLICATIONS |

| • Field transmitters |

| • HART multiplexers |

| • PLC and DCS analog I/O modules |

| • HART network connectivity |

| |

| |