|

|

• Ultra Low SSB Phase Noise Floor:-153 dBc/Hz @ 10 kHz offset @ 100 MHz Reference Frequency.

|

• Programmable Divider (N= 12 - 259) Operating up to 7 GHz

|

• Open Collector Output Buffer Amplifiers for Interfacing w/ Op-Amp Based Loop Filter

|

• Reversible Polarity PFD w/ Lock Detect Output

|

• 32 Lead 5x5mm SMT Package: 25mm2

|

|

| CATALOG |

HMC698LP5ETR COUNTRY OF ORIGIN

|

HMC698LP5ETR PARAMETRIC INFO

|

HMC698LP5ETR PACKAGE INFO

|

HMC698LP5ETR MANUFACTURING INFO

|

HMC698LP5ETR PACKAGING INFO

|

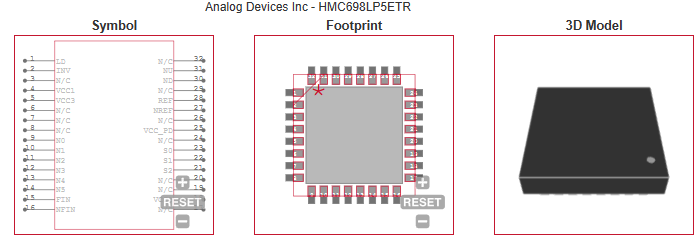

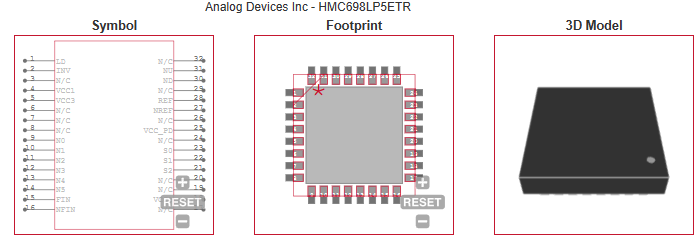

HMC698LP5ETR ECAD MODELS

|

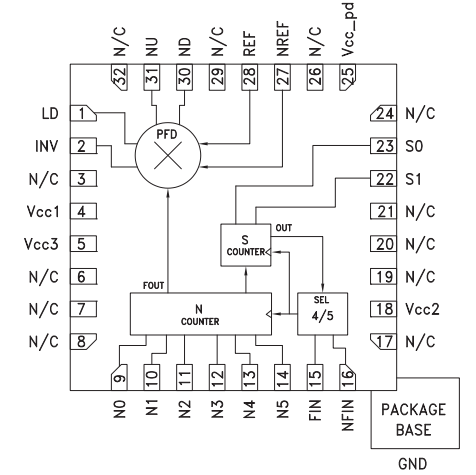

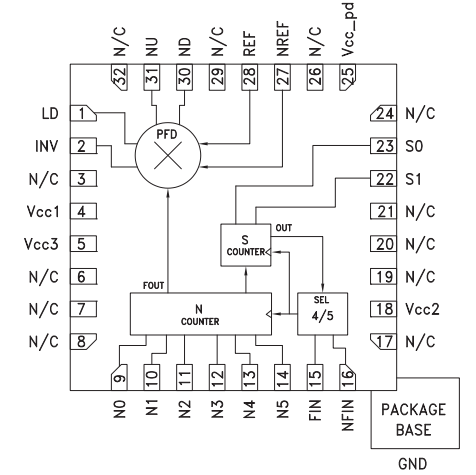

HMC698LP5ETR FUNCTIONAL DIAGRAM

|

HMC698LP5ETR APPLICATIONS

|

|

COUNTRY OF ORIGIN

|

Malaysia

|

|

PARAMETRIC INFO

|

| Number of Outputs per Chip |

1 |

| Clock Input Frequency (MHz) |

10 to 1300 |

| Input Logic Level |

CMOS|TTL |

| Minimum Operating Temperature (°C) |

-40 |

| Maximum Operating Temperature (°C) |

85 |

| Input Signal Type |

Differential |

| Output Signal Type |

Single-Ended |

| Hitless Protection Switching |

No |

| Frequency Margining |

No |

| Programmability |

Yes |

| Minimum Storage Temperature (°C) |

-65 |

| Maximum Storage Temperature (°C) |

150 |

| Minimum Operating Supply Voltage (V) |

4.75 |

| Typical Operating Supply Voltage (V) |

5 |

| Maximum Operating Supply Voltage (V) |

5.25 |

| Number of Clock Inputs |

1 |

| Spread Spectrum |

No |

| Maximum Supply Current (mA) |

340 |

|

|

PACKAGE INFO

|

| Supplier Package |

LFCSP EP |

| Basic Package Type |

Non-Lead-Frame SMT |

| Pin Count |

32 |

| Lead Shape |

No Lead |

| PCB |

32 |

| Tab |

N/R |

| Pin Pitch (mm) |

0.5 |

| Package Length (mm) |

5 |

| Package Width (mm) |

5 |

| Package Height (mm) |

0.88 |

| Package Diameter (mm) |

N/R |

| Package Overall Length (mm) |

5 |

| Package Overall Width (mm) |

5 |

| Package Overall Height (mm) |

0.9 |

| Seated Plane Height (mm) |

0.9 |

| Mounting |

Surface Mount |

| Package Weight (g) |

N/A |

| Package Material |

Plastic |

| Package Description |

Lead Frame Chip Scale Package, Exposed Pad |

| Package Family Name |

CSP |

| Jedec |

MO-220VHHD-4 |

| Package Outline |

Link to Datasheet |

|

|

MANUFACTURING INFO

|

| MSL |

1 |

| Maximum Reflow Temperature (°C) |

260 |

| Reflow Solder Time (Sec) |

30 |

| Number of Reflow Cycle |

3 |

| Standard |

J-STD-020D |

| Maximum Wave Temperature (°C) |

N/R |

| Wave Solder Time (Sec) |

N/R |

| Lead Finish(Plating) |

Matte Sn annealed |

| Number of Wave Cycles |

N/R |

|

|

PACKAGING INFO

|

| Packaging Suffix |

TR |

| Packaging |

Tape and Reel |

| Quantity Of Packaging |

500 |

| Reel Diameter (in) |

13 |

|

|

| ECAD MODELS |

|

|

FUNCTIONAL DIAGRAM

|

|

|

APPLICATIONS

|

• Satellite Communication Systems

|

• Point-to-Point Radios

|

• Military Applications

|

• Sonet Clock Generation

|

| |