|

|

• HIGH SPEED: tPD = 9 ns (TYP.) at VCC = 6V

|

• LOW POWER DISSIPATION:ICC = 1µA(MAX.) at TA=25°C

|

• HIGH NOISE IMMUNITY:VNIH = VNIL = 28 % VCC (MIN.)

|

• SYMMETRICAL OUTPUT IMPEDANCE:|IOH| = IOL = 4mA (MIN)

|

• BALANCED PROPAGATION DELAYS:tPLH ≅ tPHL

|

• WIDE OPERATING VOLTAGE RANGE: VCC (OPR) = 2V to 6V

|

• PIN AND FUNCTION COMPATIBLE WITH 74 SERIES 4075

|

|

| CATALOG |

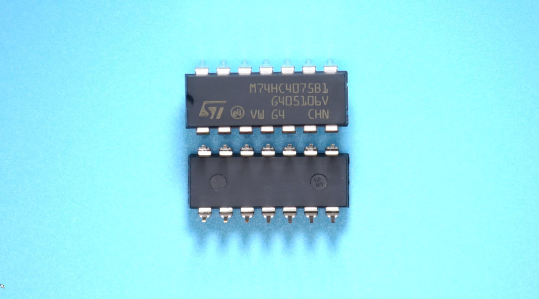

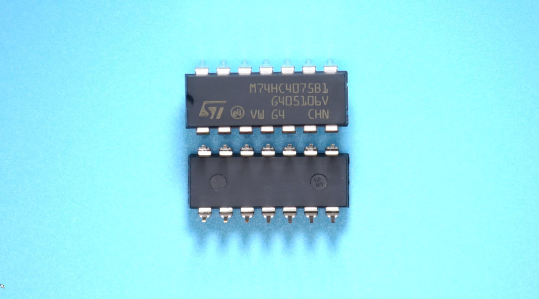

M74HC4075B1R COUNTRY OF ORIGIN

|

M74HC4075B1R PARAMETRIC INFO

|

M74HC4075B1R PACKAGE INFO

|

M74HC4075B1R MANUFACTURING INFO

|

M74HC4075B1R PACKAGING INFO

|

M74HC4075B1R ECAD MODELS

|

|

COUNTRY OF ORIGIN

|

Morocco

|

Korea (Republic of)

|

China

|

Singapore

|

Malaysia

|

Philippines

|

India

|

|

PARAMETRIC INFO

|

| Logic Family |

HC |

| Logic Function |

OR |

| Number of Element Inputs |

3-IN |

| Number of Element Outputs |

1 |

| Number of Elements per Chip |

3 |

| Number of Output Enables per Element |

0 |

| Number of Selection Inputs per Element |

0 |

| Process Technology |

CMOS |

| Minimum Operating Supply Voltage (V) |

2 |

| Maximum Operating Supply Voltage (V) |

6 |

| Typical Operating Supply Voltage (V) |

2.5|3.3|5 |

| Maximum High Level Output Current (mA) |

-5.2 |

| Maximum Low Level Output Current (mA) |

5.2 |

| Minimum Operating Temperature (°C) |

-55 |

| Maximum Operating Temperature (°C) |

125 |

| Minimum Storage Temperature (°C) |

-65 |

| Maximum Storage Temperature (°C) |

150 |

| Maximum Propagation Delay Time @ Maximum CL (ns) |

80@2V|16@4.5V|14@6V |

| Absolute Propagation Delay Time (ns) |

120 |

| Propagation Delay Test Condition (pF) |

50 |

| Maximum Quiescent Current (uA) |

1 |

|

|

PACKAGE INFO

|

| Supplier Package |

PDIP |

| Basic Package Type |

Through Hole |

| Pin Count |

14 |

| Lead Shape |

Through Hole |

| PCB |

14 |

| Tab |

N/R |

| Pin Pitch (mm) |

2.54 |

| Package Length (mm) |

20(Max) |

| Package Width (mm) |

7.1(Max) |

| Package Height (mm) |

5.1(Max) - 0.51(Min) |

| Package Diameter (mm) |

N/R |

| Seated Plane Height (mm) |

5.1(Max) |

| Mounting |

Through Hole |

| Package Material |

Plastic |

| Package Description |

Plastic Dual In Line Package |

| Package Family Name |

DIP |

| Jedec |

N/A |

| Package Outline |

Link to Datasheet |

|

|

MANUFACTURING INFO

|

| MSL |

N/R |

| Maximum Reflow Temperature (°C) |

N/R |

| Reflow Solder Time (Sec) |

N/R |

| Number of Reflow Cycle |

N/R |

| Standard |

IPC-1752 |

| Reflow Temp. Source |

Link to Datasheet |

| Maximum Wave Temperature (°C) |

260 |

| Wave Solder Time (Sec) |

10 |

| Wave Temp. Source |

Link to Datasheet |

| Lead Finish(Plating) |

Au |

| Under Plating Material |

Pd over Ni |

| Terminal Base Material |

Cu Alloy |

| Shelf Life Period |

2 Years |

| Shelf Life Condition |

N/A |

| Number of Wave Cycles |

2 |

|

|

PACKAGING INFO

|

| Packaging |

Tube |

| Quantity Of Packaging |

25 |

| Packaging Document |

Link to Datasheet |

|

|

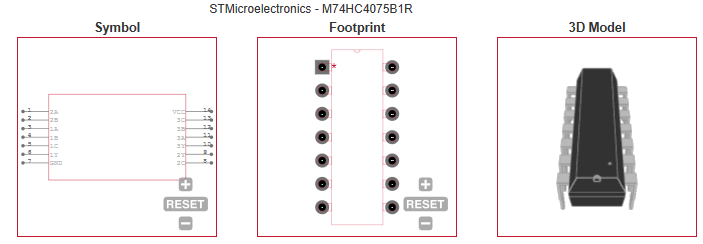

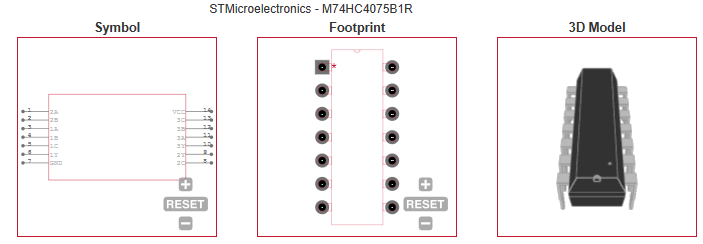

ECAD MODELS

|

|

| |