|

| |

• Designed for 1.65 V to 5.5 V VCC Operation

|

• 3.7 ns tPD at VCC = 5 V (typ)

|

• Input/Output Overvoltage Tolerant up to 5.5 V

|

| • IOFF Supports Partial Power Down Protection |

| • Source/Sink 24 mA at 3.0 V |

| • Available in SC−88A, SC−74A, SOT−553, SOT−953 and UDFN6 Packages |

| • Chip Complexity < 100 FETs |

| • −Q Suffix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC−Q100 Qualified and PPAP Capable |

| • These Devices are Pb−Free, Halogen Free/BFR Free and are RoHS Compliant |

| |

| CATALOG |

| NL17SZ17DFT2G COUNTRY OF ORIGIN |

NL17SZ17DFT2G PARAMETRIC INFO

|

NL17SZ17DFT2G PACKAGE INFO

|

NL17SZ17DFT2G MANUFACTURING INFO

|

NL17SZ17DFT2G PACKAGING INFO

|

NL17SZ17DFT2G EACD MODELS

|

|

| COUNTRY OF ORIGIN |

| Malaysia |

| China |

|

PARAMETRIC INFO

|

| Process Technology |

CMOS |

| Logic Family |

LCX |

| Logic Function |

Schmitt Trigger Buffer |

| Input Signal Type |

Single-Ended |

| Polarity |

Non-Inverting |

| Tolerant I/Os (V) |

5.5 |

| Bus Hold |

No |

| Number of Elements per Chip |

1 |

| Number of Channels per Chip |

1 |

| Number of Output Enables per Chip |

0 |

| Number of Input Enables per Chip |

0 |

| Number of Inputs per Chip |

1 |

| Number of Outputs per Chip |

1 |

| Minimum Operating Supply Voltage (V) |

1.65 |

| Maximum Operating Supply Voltage (V) |

5.5 |

| Typical Operating Supply Voltage (V) |

1.8|2.5|3.3|5 |

| Minimum Operating Temperature (°C) |

-55 |

| Maximum Operating Temperature (°C) |

125 |

| Minimum Storage Temperature (°C) |

-65 |

| Maximum Storage Temperature (°C) |

150 |

| Maximum Power Dissipation (mW) |

332 |

| Maximum Propagation Delay Time @ Maximum CL (ns) |

7.2@3V to 3.6V|5.9@4.5V to 5.5V |

| Absolute Propagation Delay Time (ns) |

15.6 |

| Propagation Delay Test Condition (pF) |

50 |

| Maximum High Level Output Current (mA) |

-32 |

| Maximum Low Level Output Current (mA) |

32 |

| Maximum Quiescent Current (uA) |

1 |

|

|

PACKAGE INFO

|

| Supplier Package |

SC-88A |

| Basic Package Type |

Lead-Frame SMT |

| Pin Count |

5 |

| Lead Shape |

Gull-wing |

| PCB |

5 |

| Tab |

N/R |

| Pin Pitch (mm) |

0.65 |

| Package Length (mm) |

2.2(Max) |

| Package Width (mm) |

1.35(Max) |

| Package Height (mm) |

1(Max) |

| Package Diameter (mm) |

N/R |

| Package Overall Length (mm) |

2.2(Max) |

| Package Overall Width (mm) |

2.2(Max) |

| Package Overall Height (mm) |

1.1(Max) |

| Seated Plane Height (mm) |

1.1(Max) |

| Mounting |

Surface Mount |

| Package Weight (g) |

N/A |

| Package Material |

Plastic |

| Package Description |

Small Outline Transistor |

| Package Family Name |

SOT |

| Jedec |

N/A |

| Package Outline |

Link to Datasheet |

|

|

MANUFACTURING INFO

|

| MSL |

1 |

| Maximum Reflow Temperature (°C) |

260 |

| Reflow Solder Time (Sec) |

30 |

| Number of Reflow Cycle |

3 |

| Standard |

N/A |

| Reflow Temp. Source |

Link to Datasheet |

| Maximum Wave Temperature (°C) |

N/R |

| Wave Solder Time (Sec) |

N/R |

| Lead Finish(Plating) |

Matte Sn annealed |

| Under Plating Material |

N/A |

| Terminal Base Material |

FeNi Alloy |

| Number of Wave Cycles |

N/R |

|

|

PACKAGING INFO

|

| Packaging Suffix |

T2 |

| Packaging |

Tape and Reel |

| Quantity Of Packaging |

3000 |

| Reel Diameter (in) |

7 |

| Reel Width (mm) |

8.4(Min) |

| Tape Pitch (mm) |

4 |

| Tape Width (mm) |

8 |

| Feed Hole Pitch (mm) |

4 |

| Hole Center to Component Center (mm) |

2 |

| Component Orientation |

Q3 |

| Packaging Document |

Link to Datasheet |

| Tape Type |

Embossed |

|

|

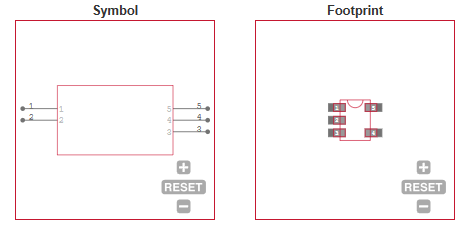

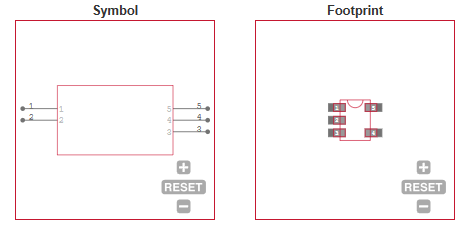

ECAD MODELS

|

|

| |