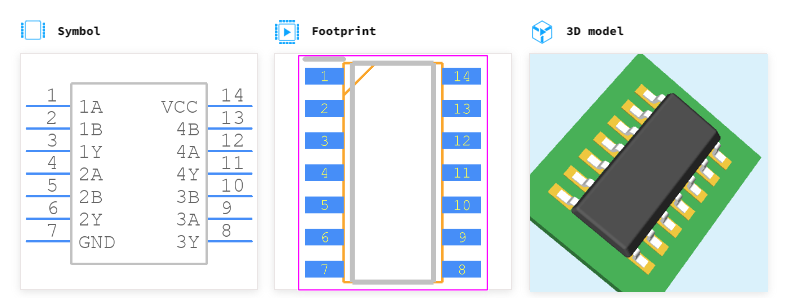

| Logic Family |

HC |

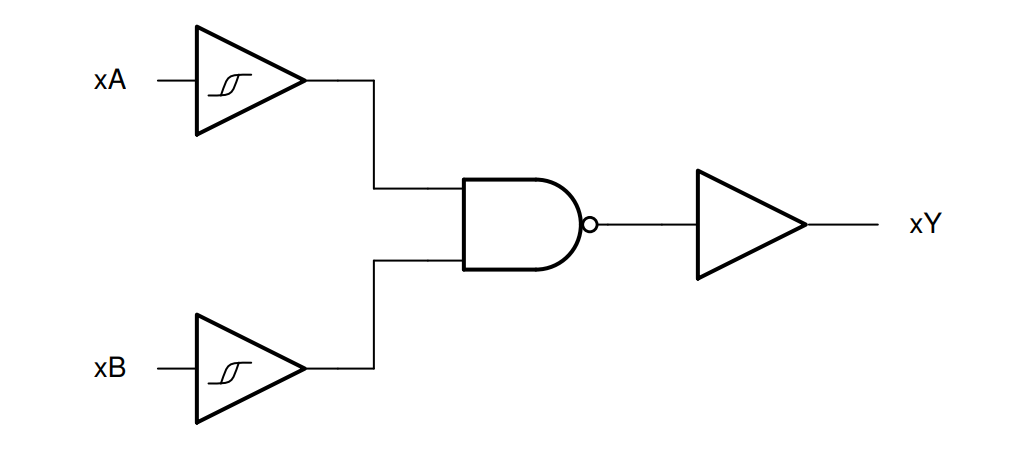

| Logic Function |

NAND |

| Number of Element Inputs |

2-IN |

| Number of Element Outputs |

1 |

| Number of Elements per Chip |

4 |

| Number of Output Enables per Element |

0 |

| Number of Selection Inputs per Element |

0 |

| Output Type |

Push-Pull |

| Process Technology |

CMOS |

| Input Type |

Schmitt Trigger |

| Minimum Operating Supply Voltage (V) |

2 |

| Maximum Operating Supply Voltage (V) |

6 |

| Typical Operating Supply Voltage (V) |

5 |

| Maximum High Level Output Current (mA) |

-5.2 |

| Maximum Low Level Output Current (mA) |

5.2 |

| Minimum Operating Temperature (°C) |

-40 |

| Maximum Operating Temperature (°C) |

85 |

| Minimum Storage Temperature (°C) |

-65 |

| Maximum Storage Temperature (°C) |

150 |

| Maximum Propagation Delay Time @ Maximum CL (ns) |

120@2V|25@4.5V|21@6V |

| Absolute Propagation Delay Time (ns) |

156 |

| Propagation Delay Test Condition (pF) |

50 |

| Maximum Quiescent Current (uA) |

2 |