|

|

• Single-Supply Voltage Translator at

5.0-V, 3.3-V, 2.5-V, and 1.8-V VCC

|

• Operating Range of 1.8 V to 5.5 V

|

• Up Translation

– 1.2 V(1) to 1.8 V at 1.8-V VCC

– 1.5 V(1) to 2.5 V at 2.5-V VCC

– 1.8 V(1) to 3.3 V at 3.3-V VCC

– 3.3 V to 5.0 V at 5.0-V VCC

|

| • Down Translation

– 3.3 V to 1.8 V at 1.8-V VCC

– 3.3 V to 2.5 V at 2.5-V VCC

– 5.0 V to 3.3 V at 3.3-V VCC |

| • Logic Output is Referenced to VCC |

| • Characterized up to 50 MHz at 3.3-V VCC |

| • 5.5 V Tolerance on Input Pins |

| • –40°C to 125°C Operating Temperature Range |

| • Pb-Free Packages Available: SC-70 (RGY)

– 3.5 × 3.5 × 1 mm

|

| • Latch-Up Performance Exceeds 250 mA Per

JESD 17 |

| • Supports Standard Logic Pinouts |

|

| CATALOG |

| SN74LV4T125RGYR COUNTRY OF ORIGIN |

SN74LV4T125RGYR PARAMETRIC INFO

|

SN74LV4T125RGYR PACKAGE INFO

|

SN74LV4T125RGYR MANUFACTURING INFO

|

SN74LV4T125RGYR PACKAGING INFO

|

SN74LV4T125RGYR ECAD MODELS

|

SN74LV4T125RGYR APPLICATIONS

|

|

| COUNTRY OF ORIGIN |

| Mexico |

| Malaysia |

| China |

|

PARAMETRIC INFO

|

| Number of Channels |

4 |

| Channel Type |

Unidirectional |

| Logic Family |

LV |

| Process Technology |

CMOS |

| Logic Function |

Voltage Level Shifter |

| Output Type |

3-State |

| Minimum Operating Temperature (°C) |

-40 |

| Maximum Operating Temperature (°C) |

125 |

| Minimum Operating Supply Voltage (V) |

1.6 |

| Maximum Operating Supply Voltage (V) |

5.5 |

| Typical Operating Supply Voltage (V) |

1.8|2.5|3.3|5 |

| Maximum High Level Output Current (mA) |

-16 |

| Maximum Low Level Output Current (mA) |

16 |

|

|

PACKAGE INFO

|

| Supplier Package |

VQFN EP |

| Basic Package Type |

Non-Lead-Frame SMT |

| Pin Count |

14 |

| Lead Shape |

No Lead |

| PCB |

14 |

| Tab |

N/R |

| Pin Pitch (mm) |

0.5 |

| Package Length (mm) |

3.65(Max) |

| Package Width (mm) |

3.65(Max) |

| Package Height (mm) |

0.95(Max) |

| Package Diameter (mm) |

N/R |

| Package Overall Length (mm) |

3.65(Max) |

| Package Overall Width (mm) |

3.65(Max) |

| Package Overall Height (mm) |

1(Max) |

| Seated Plane Height (mm) |

1(Max) |

| Mounting |

Surface Mount |

| Package Weight (g) |

N/A |

| Package Material |

Plastic |

| Package Description |

Very Thin Quad Flat No Lead Package, Exposed Pad |

| Package Family Name |

QFN |

| Jedec |

MO-241-BA |

|

|

MANUFACTURING INFO

|

| MSL |

2 |

| Maximum Reflow Temperature (°C) |

260 |

| Reflow Solder Time (Sec) |

30 |

| Number of Reflow Cycle |

3 |

| Standard |

J-STD-020D |

| Reflow Temp. Source |

Link to Datasheet |

| Maximum Wave Temperature (°C) |

N/R |

| Wave Solder Time (Sec) |

N/R |

| Lead Finish(Plating) |

Au |

| Under Plating Material |

Pd over Ni |

| Terminal Base Material |

Cu Alloy |

| Number of Wave Cycles |

N/R |

|

|

PACKAGING INFO

|

| Packaging Suffix |

R |

| Packaging |

Tape and Reel |

| Quantity Of Packaging |

3000 |

| Reel Diameter (in) |

13 |

| Reel Width (mm) |

12.4 |

| Tape Pitch (mm) |

8 |

| Tape Width (mm) |

12 |

| Component Orientation |

Q1 |

| Packaging Document |

Link to Datasheet |

|

|

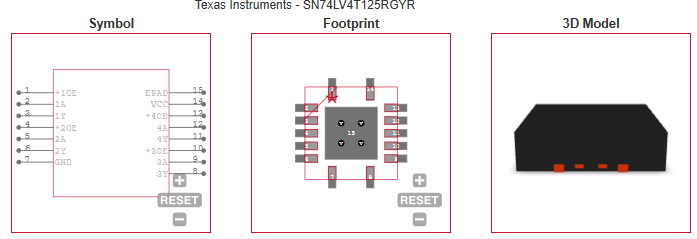

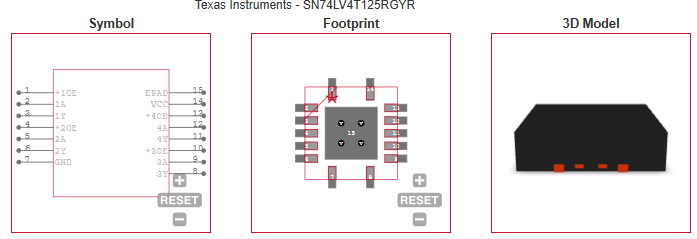

ECAD MODELS

|

|

|

APPLICATIONS

|

• Tablet

|

• Smartphone

|

| • Personal Computer |

| • Industrial Automotive |

|

| |