|

|

• Selects between 1 of 2 Inputs, and Provides 12 Precision, Low Skew LVDS Output Copies

|

• Ultra-low Jitter Design:- 130 fs RMS Phase Jitter (Typ)- 0.7 psRMS Crosstalk Induced Jitter

|

• Unique, Patent-pending 2:1 Input MUX Provides Superior Isolation to Minimize Channel-to-Channel Crosstalk

|

• CLK0 Input Features a Unique, Patent-pending Input Termination and VT Pin that Accepts ACand DC-coupled Inputs (CML, LVPEC

|

• 325 mV LVDS-compatible Output Swing

|

• Power Supply: 2.5V ±5%

|

|

| CATALOG |

SY89113UMY COUNTRY OF ORIGIN

|

SY89113UMY PARAMETRIC INFO

|

SY89113UMY PACKAGE INFO

|

SY89113UMY MANUFACTURING INFO

|

SY89113UMY PACKAGING INFO

|

SY89113UMY ECAD MODELS

|

SY89113UMY APPLICATIONS

|

|

COUNTRY OF ORIGIN

|

Philippines

|

Thailand

|

|

PARAMETRIC INFO

|

| Type |

Fanout Buffer |

| Fanout |

1:12 |

| Number of Outputs per Chip |

12 |

| Input Logic Level |

CML|CMOS|HSTL|LVDS|LVPECL|TTL |

| Output Logic Level |

LVDS |

| Minimum Operating Supply Voltage (V) |

2.375 |

| Maximum Operating Supply Voltage (V) |

2.625 |

| Minimum Output Frequency (MHz) |

1000 |

| Minimum Input Frequency (MHz) |

1000 |

| Output Signal Type |

Differential |

| Maximum Output Skew (ps) |

25 |

| Minimum Operating Temperature (°C) |

-40 |

| Maximum Operating Temperature (°C) |

85 |

| Supplier Temperature Grade |

Industrial |

| Minimum Storage Temperature (°C) |

-65 |

| Maximum Storage Temperature (°C) |

150 |

| Typical Operating Supply Voltage (V) |

2.5 |

| Maximum Quiescent Current (mA) |

330 |

| Number of Clock Inputs |

2 |

| Spread Spectrum |

No |

| Input Signal Type |

Differential |

| Power Supply Type |

Single |

| Configuration |

1 x 2:1 |

| Maximum Propagation Delay Time @ Maximum CL (ns) |

1.2@2.375V to 2.625V |

| Absolute Propagation Delay Time (ns) |

1.2 |

|

|

PACKAGE INFO

|

| Supplier Package |

QFN EP |

| Basic Package Type |

Non-Lead-Frame SMT |

| Pin Count |

44 |

| Lead Shape |

No Lead |

| PCB |

44 |

| Tab |

N/R |

| Package Length (mm) |

7 |

| Package Width (mm) |

7 |

| Package Height (mm) |

0.85(Max) |

| Package Diameter (mm) |

N/R |

| Mounting |

Surface Mount |

| Package Description |

Quad Flat No Lead Package, Exposed Pad |

| Package Family Name |

QFN |

| Package Outline |

Link to Datasheet |

|

|

MANUFACTURING INFO

|

| MSL |

2 |

| Maximum Reflow Temperature (°C) |

260 |

| Reflow Solder Time (Sec) |

20 |

| Reflow Temp. Source |

Link to Datasheet |

| Maximum Wave Temperature (°C) |

N/R |

| Wave Solder Time (Sec) |

N/R |

| Lead Finish(Plating) |

Matte Sn annealed |

| Under Plating Material |

N/A |

| Terminal Base Material |

Cu Alloy |

|

|

PACKAGING INFO

|

| Packaging |

Tray |

| Quantity Of Packaging |

260 |

|

|

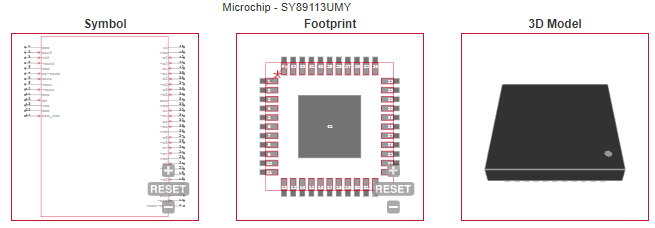

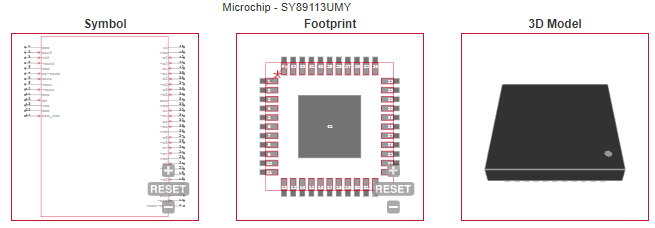

ECAD MODELS

|

|

|

| APPLICATIONS |

| • Multi-processor Server |

| • SONET/SDH Clock/Data Distribution |

| • Fibre Channel Distribution |

| • Gigabit Ethernet Clock Distribution |

| |